本文对ARM Neoverse系列服务器CPU做一些初步调研,并尝试比较服务器CPU与手机AP CPU的异同。

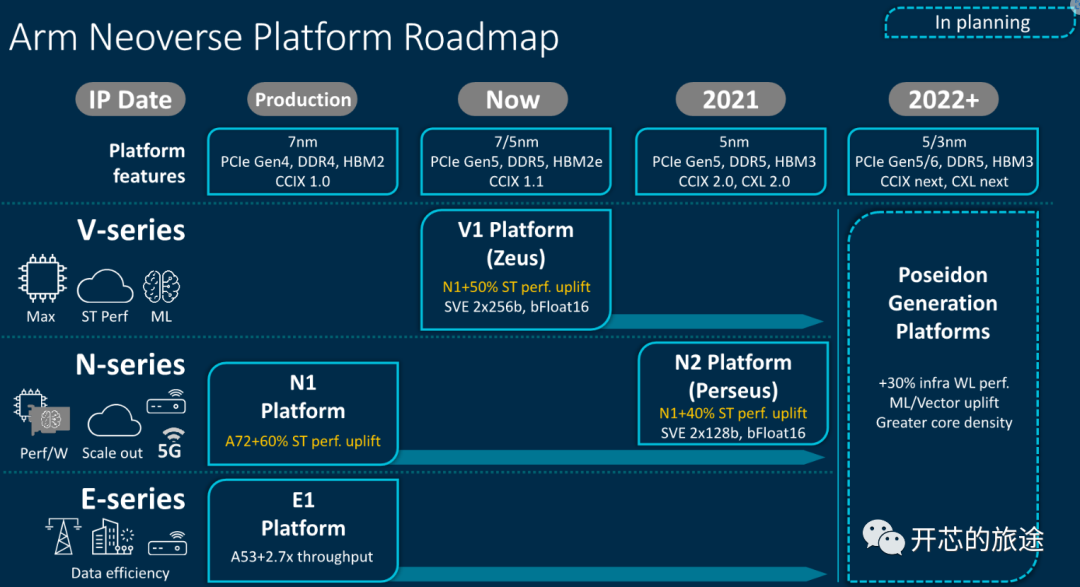

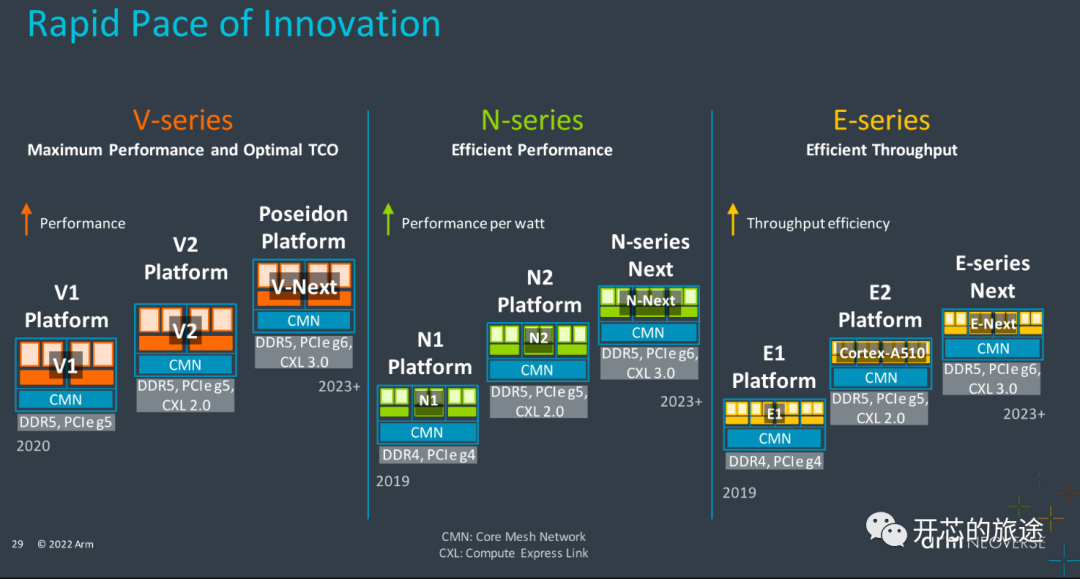

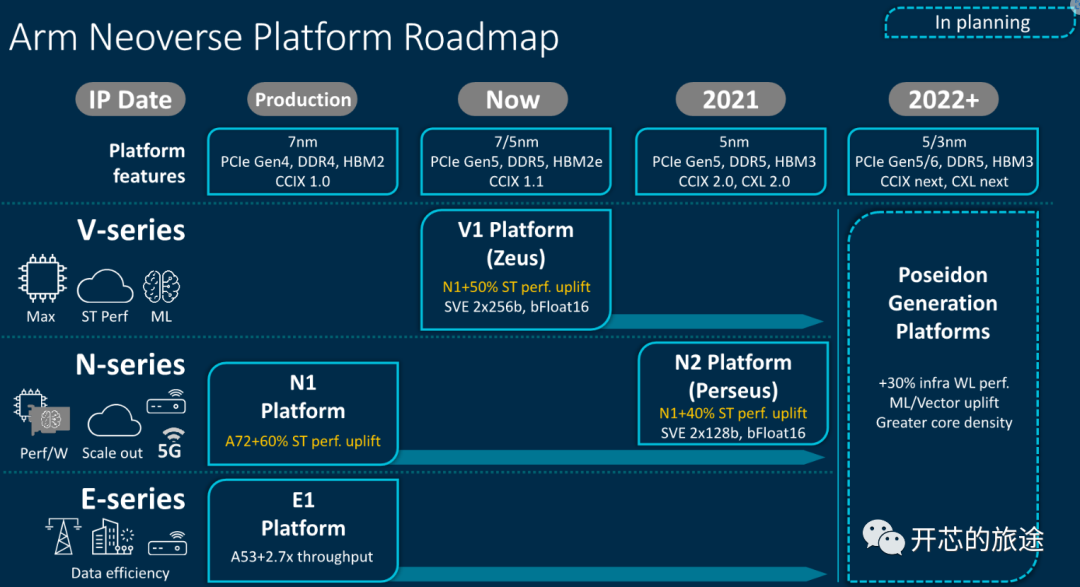

首先看一下ARM Neoverse系列CPU的全家福,其中一些主要的CPU会在下文重点介绍。

(图源:Anandtech)

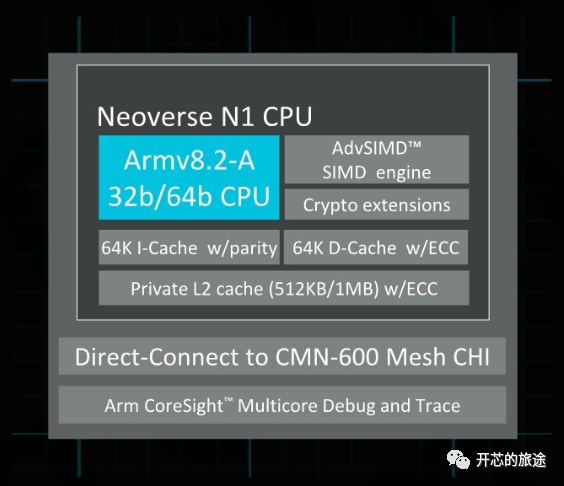

1. ARM Neoverse N1

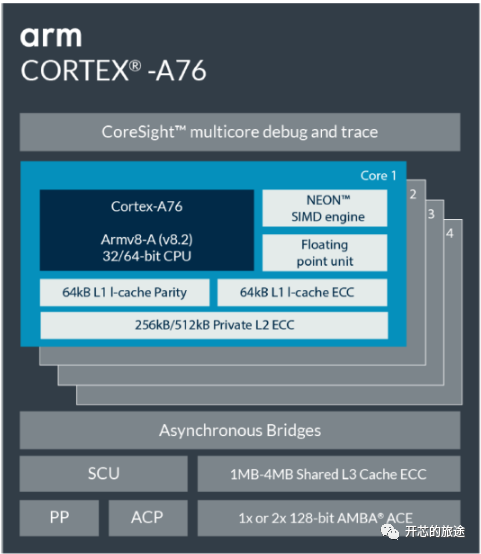

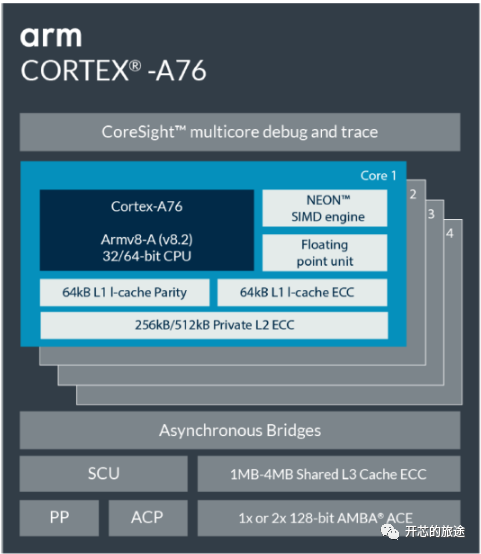

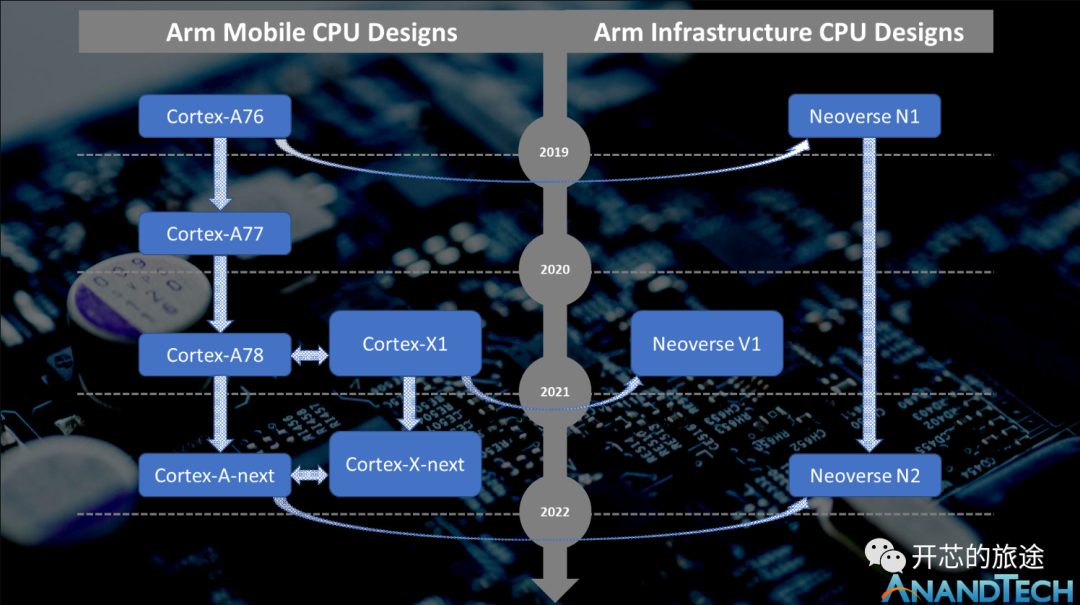

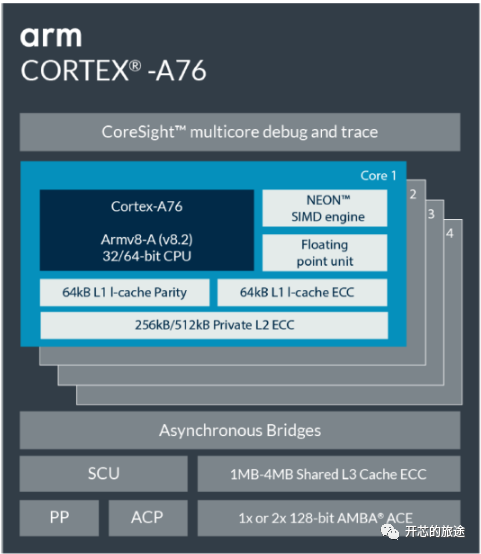

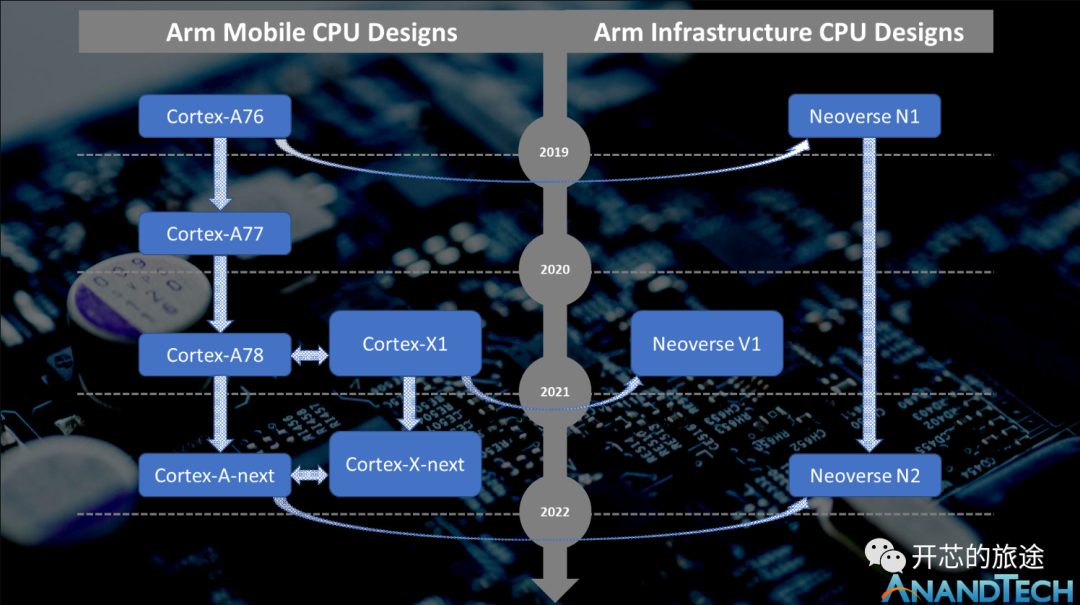

ARM在2019年2月首次发布面向服务器的CPU产品:ARM Neoverse N1。Neoverse N1跟Cortex-A76是同一时代的产品,所以下面重点对比Neoverse N1与Cortex-A76的异同。

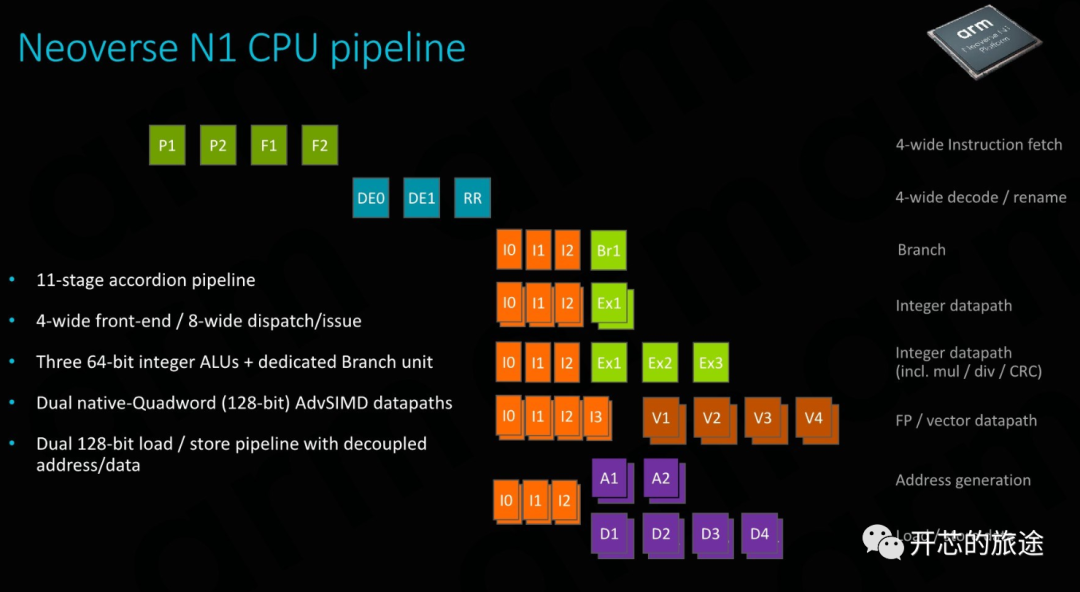

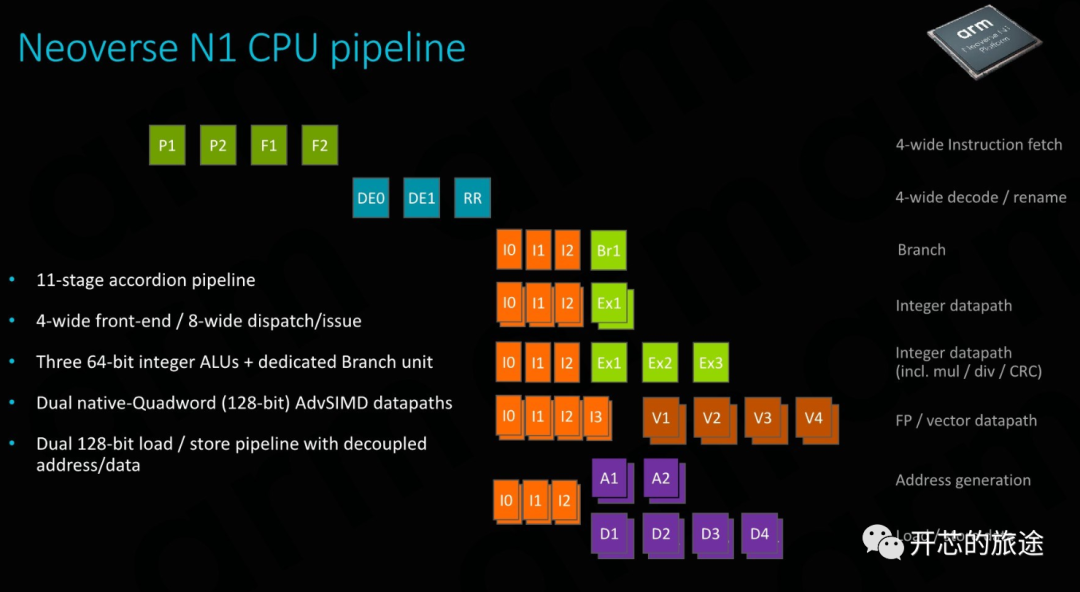

1.1 流水线结构

从CPU core的流水线结构上来看,Neoverse N1采用最短11级的流水线,取指/译码的宽度为4,具有3个64-bit整数ALU和1个Branch单元,2个128-bit的Advanced SIMD(负责浮点/向量运算)单元,以及两个128-bit Load/Store的单元。从流水线结构上看,与Cortex-A76没有明显差异。

(图源:Anandtech)

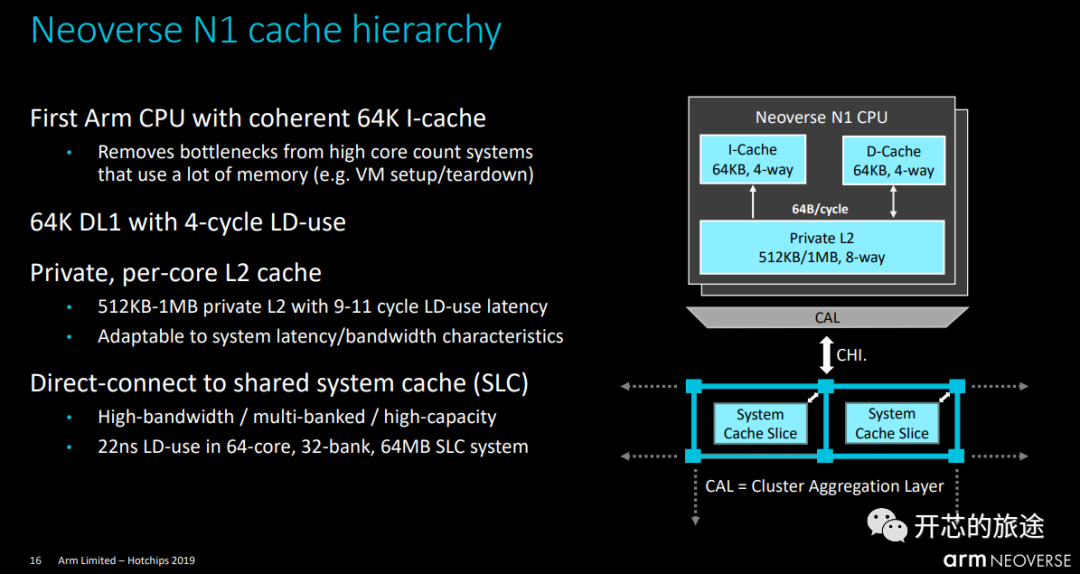

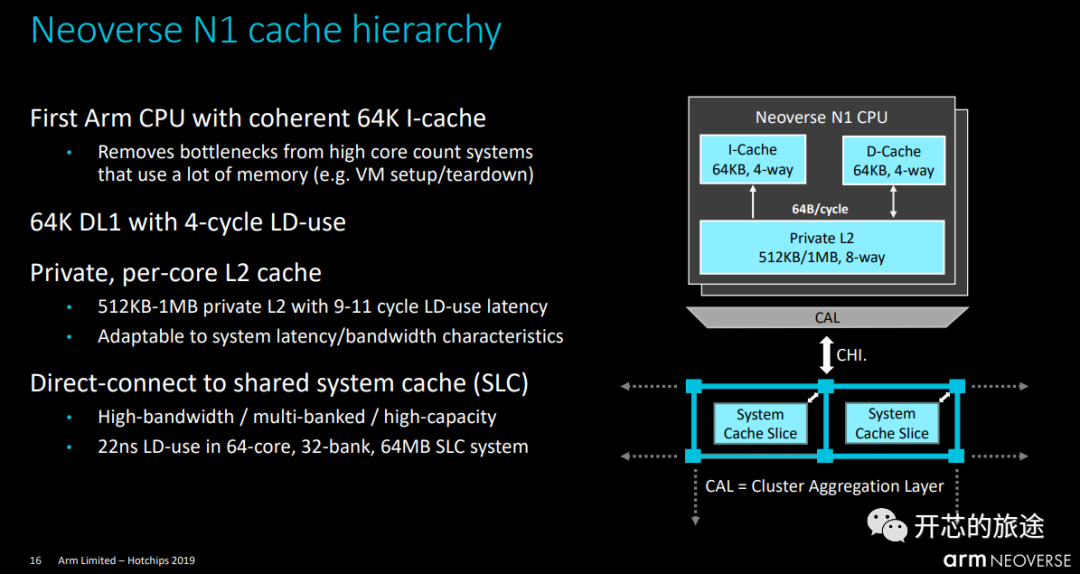

1.2 Cache

在cache结构上,Neoverse N1的Instruction cache可以通过配置选择是否支持硬件一致性,这个配置选项是针对服务器这种多核的应用场景所添加的。ARM在架构上并不要求Instruction cache具有硬件一致性的能力。所以对于之前的ARM CPU,如果memory里面的指令被修改了,那么软件需要进行cache maintenance操作(如I cache invalidation)。这些cache maintenance操作通常会以广播的形式发给与当前core保持一致性的其他所有core。这种广播的形式对于核数较多的系统而言会造成较大的性能开销。而在服务器场景下,ARM提到VM的setup/teardown会导致memory里面的指令被修改的情况。

(图源:ARM, Hotchips 2019)

如果配置Neoverse N1支持I-cache的硬件一致性,则节省了软件进行I-cache maintenance的开销。为了保证软件的兼容性,在支持I-cache硬件一致性的Neoverse N1上,如果执行的旧版本软件依然执行I-cache maintenance指令,Neoverse N1会将这些指令当作“No operation”(即NOP)来处理。对于新开发的软件,Neoverse N1提供一个寄存器bit可以供软件查询当前Neoverse N1是否配置了I-cache的硬件一致性选项。(以上内容参考ARM的白皮书《The Arm Neoverse N1 Platform: Building Blocks for the Next-Gen Cloud-to-Edge Infrastructure SoC》)

另外Neoverse N1可配置的L2 cache size与A76存在差异。Neoverse N1的L2 cache size为256KB ~ 1024KB,而Cortex-A76的L2 cache size为128KB ~ 512KB。如果Neoverse N1配置支持I-cache的硬件一致性,那么L1 Instruction cache会与L2 cache保持完全的inclusive关系,即所有L1 Instuction cache中的内容都必须放在L2 cache里面,此时ARM建议L2 cache size配置成1024KB。如果配置成512KB,由于被L1 instruction cache的严格inclusive关系占用部分cache空间,可能会有1% ~ 2%的性能损失。(以上内容参考ARM Neoverse N1 Technical Reference Manual)

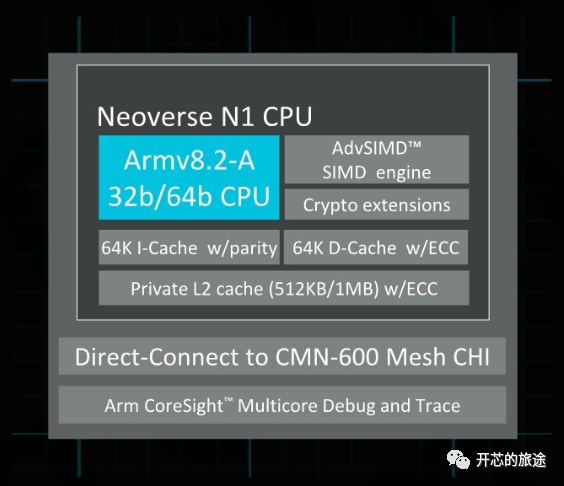

1.3 Neoverse N1与下游的连接

从集成的角度,ARM Neoverse N1可以选择以Direct-Connect的形式直接连接到CMN-600总线上。

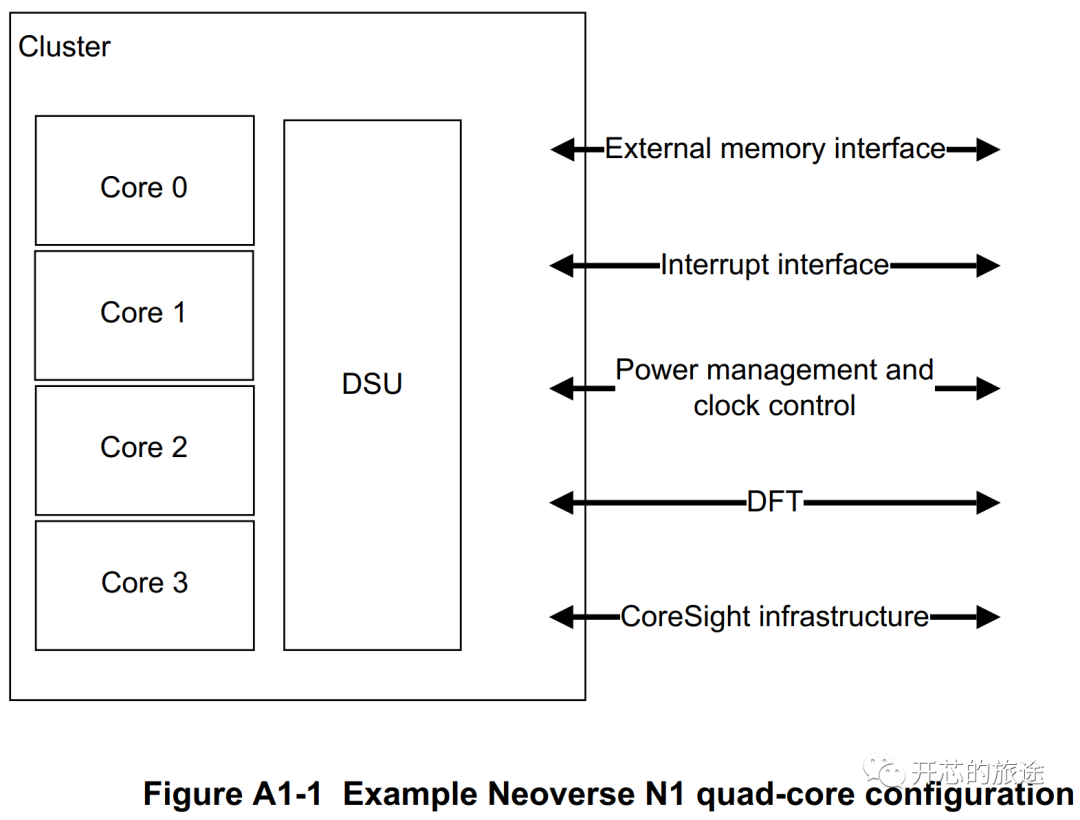

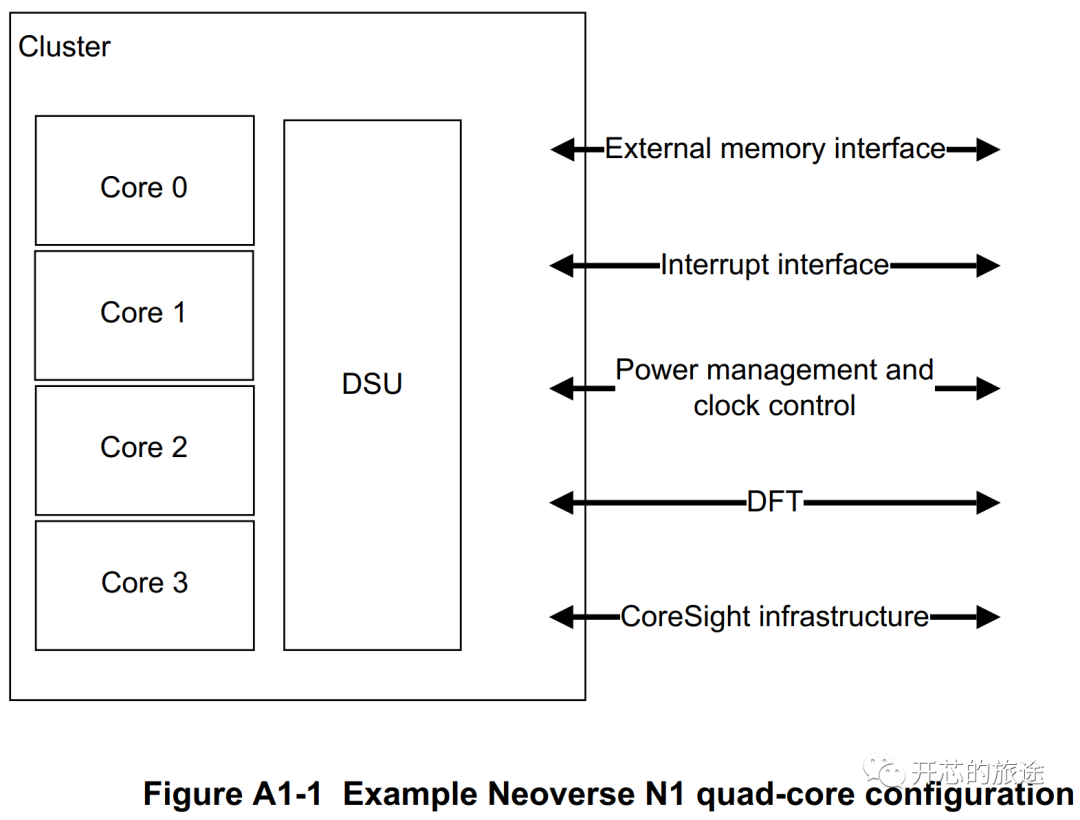

(图源:Anandtech)

Direct Connect是ARM DSU (DynamIQ Shared Unit)的一个配置选项,当DSU配置成Direct Connect这种模式的时候,DSU内部的L3 cache,snoop filter和Snoop Control Unit (SCU)将不再存在。由于此时DSU内部没有任何负责一致性的逻辑,所以一个DSU cluster最多只支持一个core。多个DSU cluster之间的一致性由DSU外部的一致性总线(如CMN600)来维护。由于Direct Connect模式下DSU内部没有L3 cache,所以通常需要外部的一致性总线(如CMN600)配置一定量的system cache来满足CPU的性能需求。

作为对比,可以看一下A76的DSU结构,DSU内部的L3 cache、Snoop Control Unit等模块通常都是存在的。从A76的Technical Reference Manual里面也没有看到描述A76支持像Neoverse N1那样的Direct Connect模式:

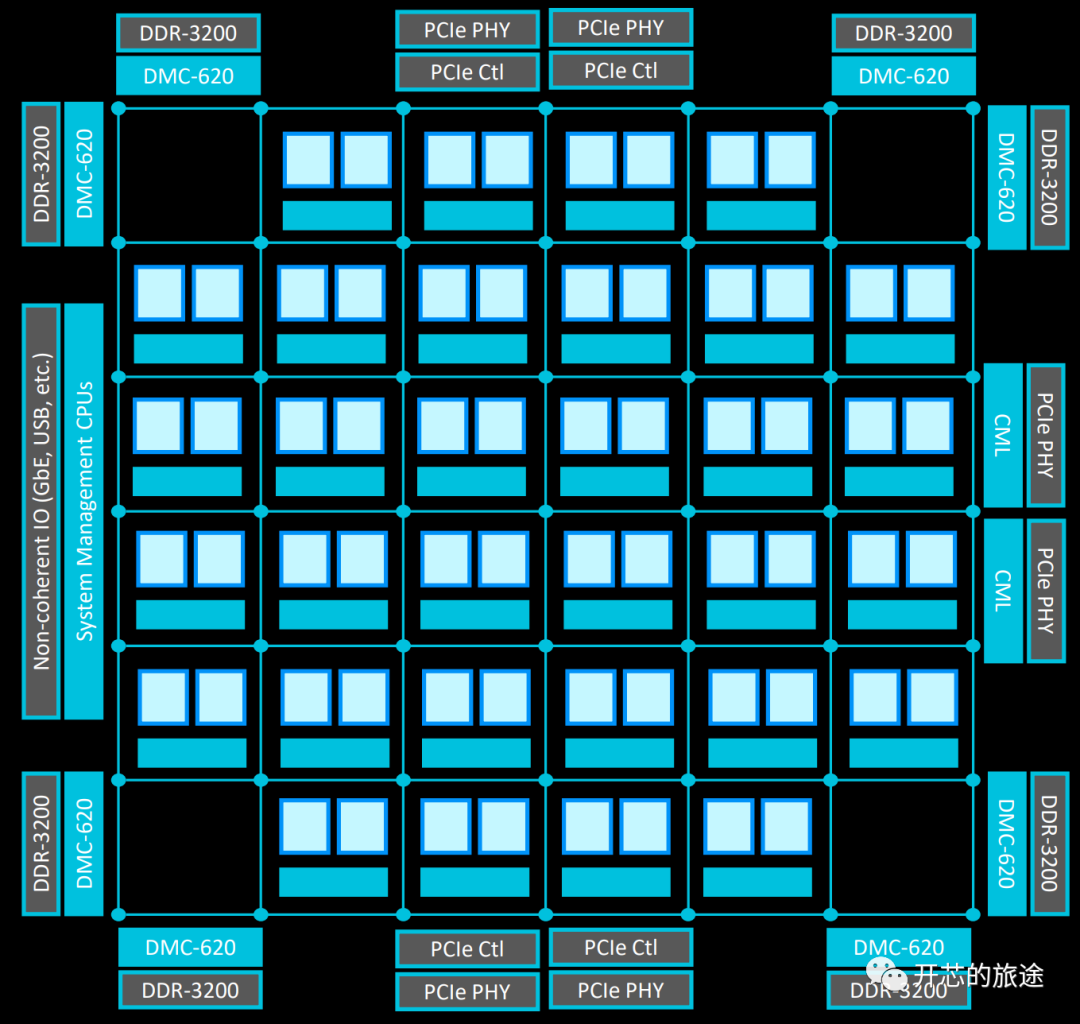

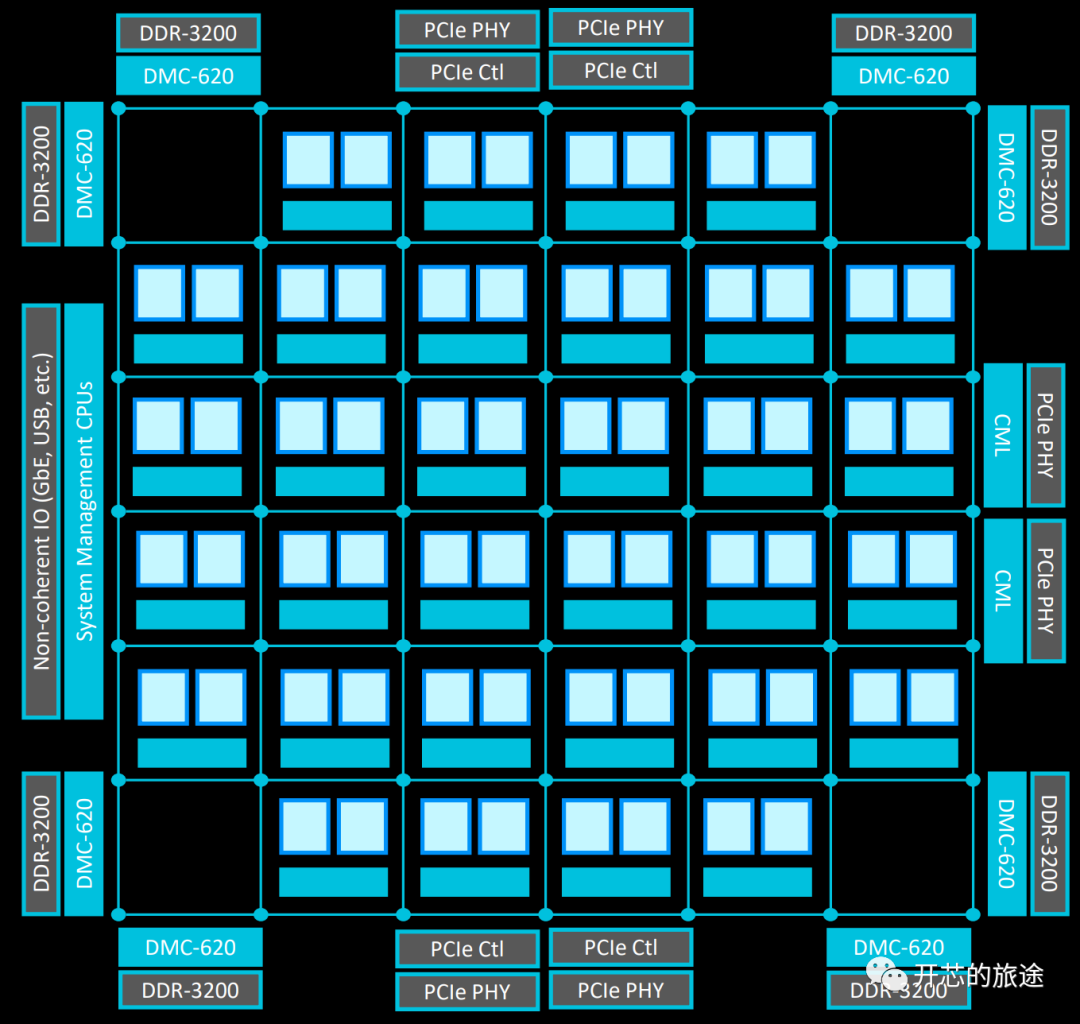

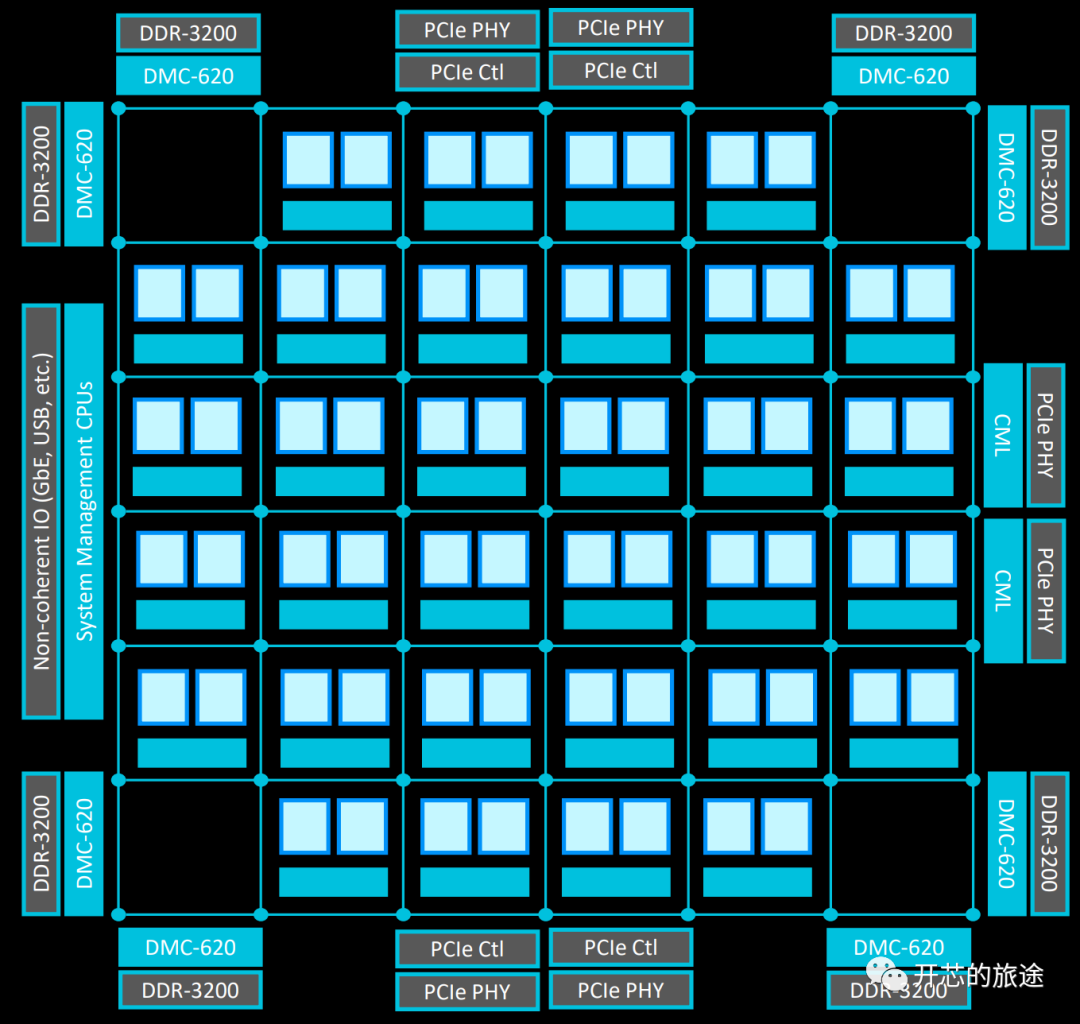

除了Direct Connect这种配置外,Neoverse N1 IP本身也支持DSU cluster里面最多配置4个Neoverse N1,然后在DSU内部把这几个core的一致性处理做掉,然后多个DSU之间再通过一致性总线相连。下图就是DSU里面配置4个Neoverse N1 core的一个例子:下面是ARM的一个基于Neoverse N1 CPU的大型SOC芯片的参考设计。使用了64个Nerverse N1 CPU,利用CMN-600一致性总线进行互联,再配合DDR controller、PCIe controller等IP组成整个SOC。

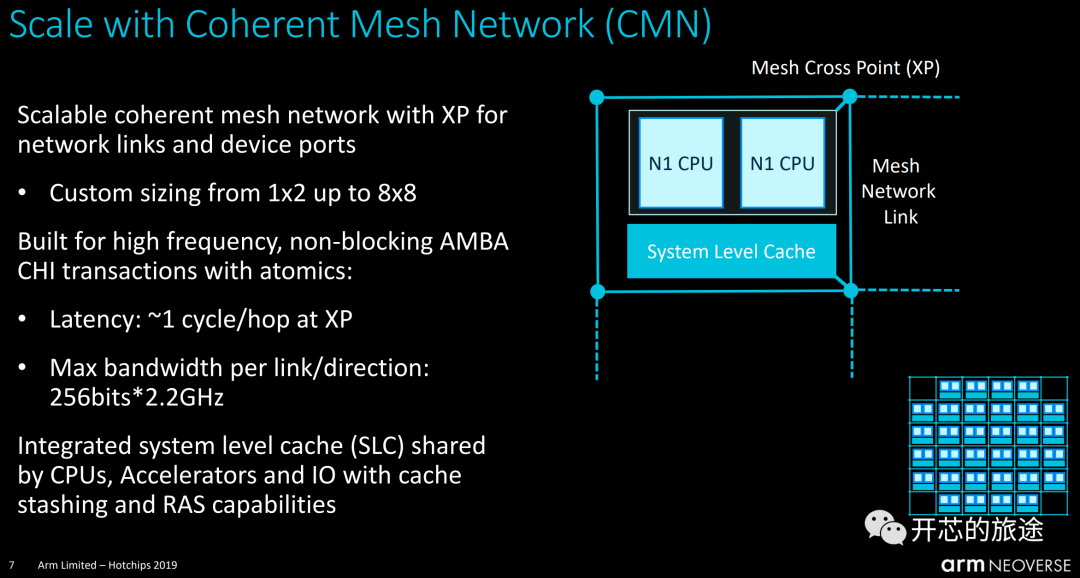

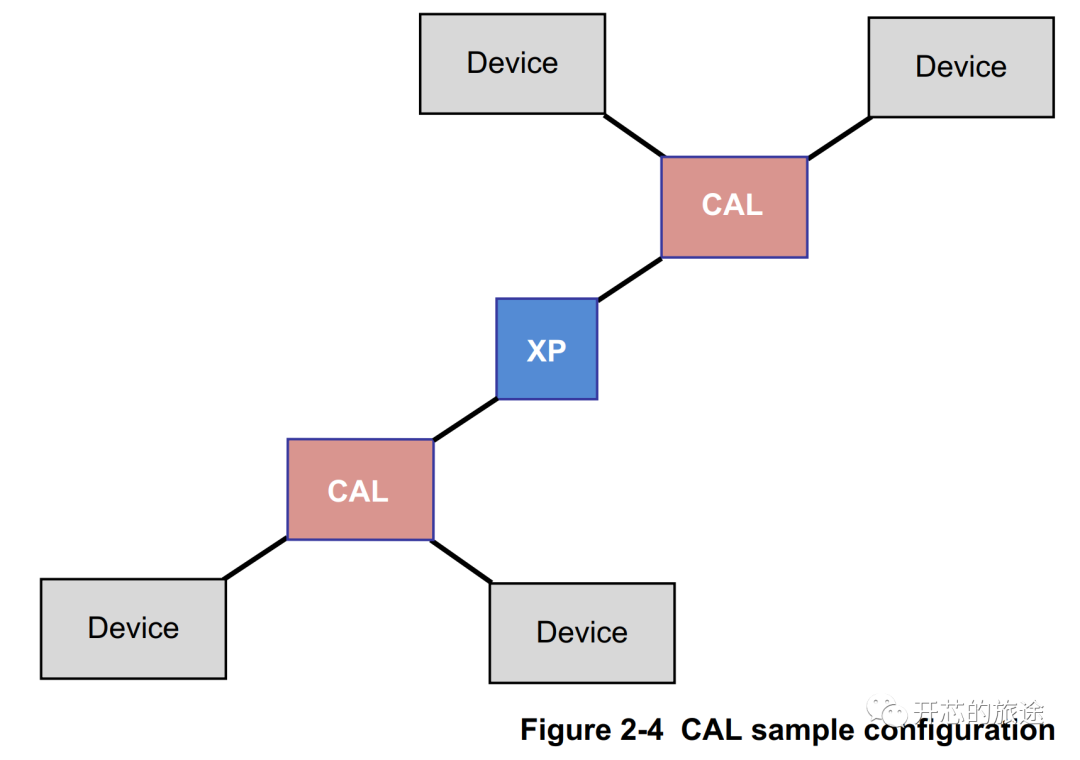

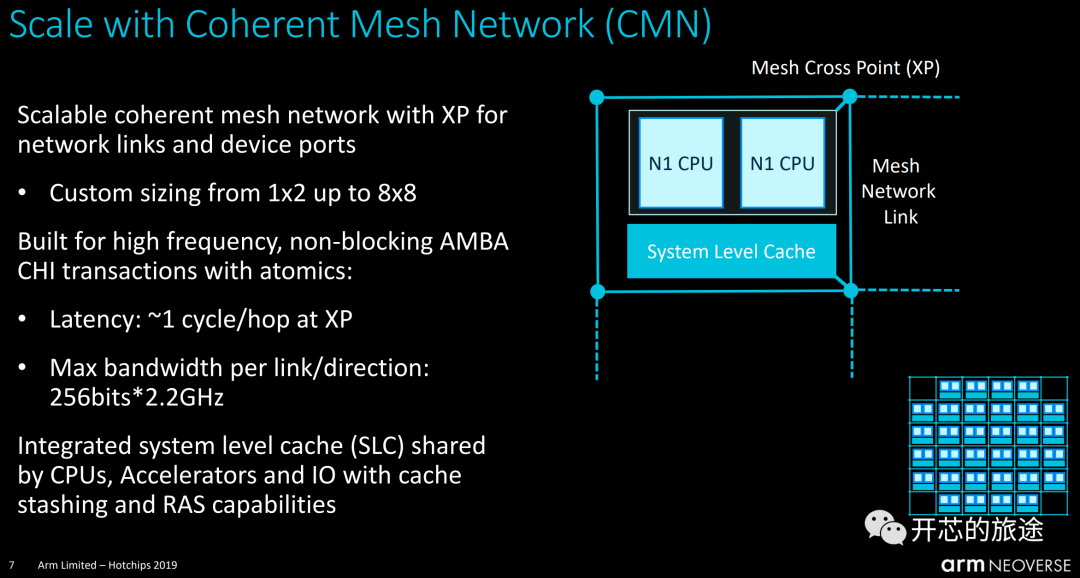

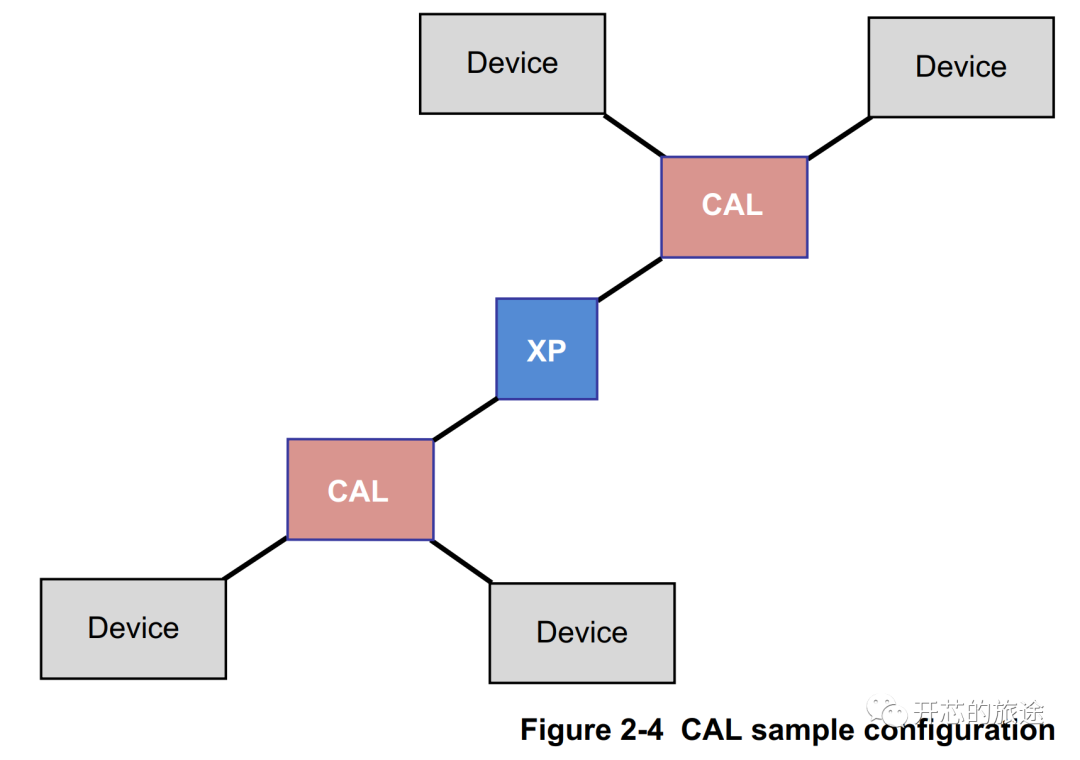

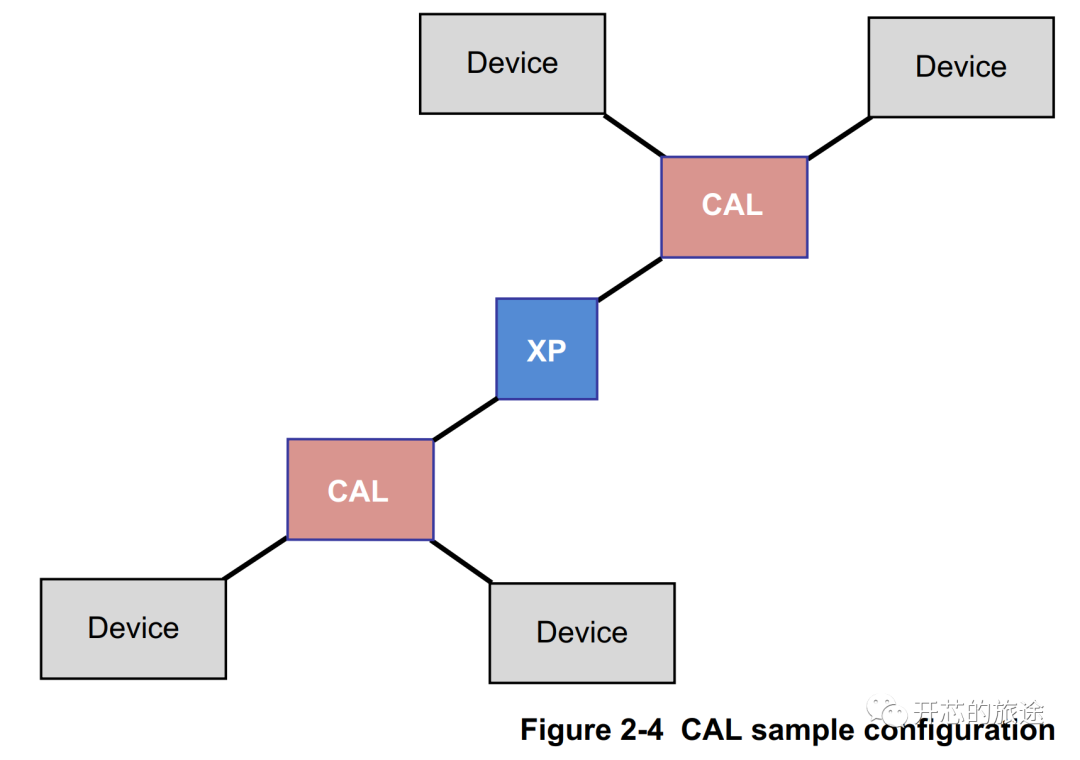

上图中有大量的单元挂在mesh的节点上,在下图中可以看到这些挂在Mesh网络中的Cross Point(XP)节点上的单元为2个N1 CPU,和System Level Cache。CMN可以支持从1x2到8x8的mesh结构,在latency上,每一个cycle可以进行一次hop,即从一个XP跳到相邻的XP:两个N1 CPU连接到XP上的时候可以配置成Direct Connect形式,利用CMN600里面的CAL(Component Aggregation Layer)组件,能够将最多两个相同的RNF(Request Node Full)连接到XP上。

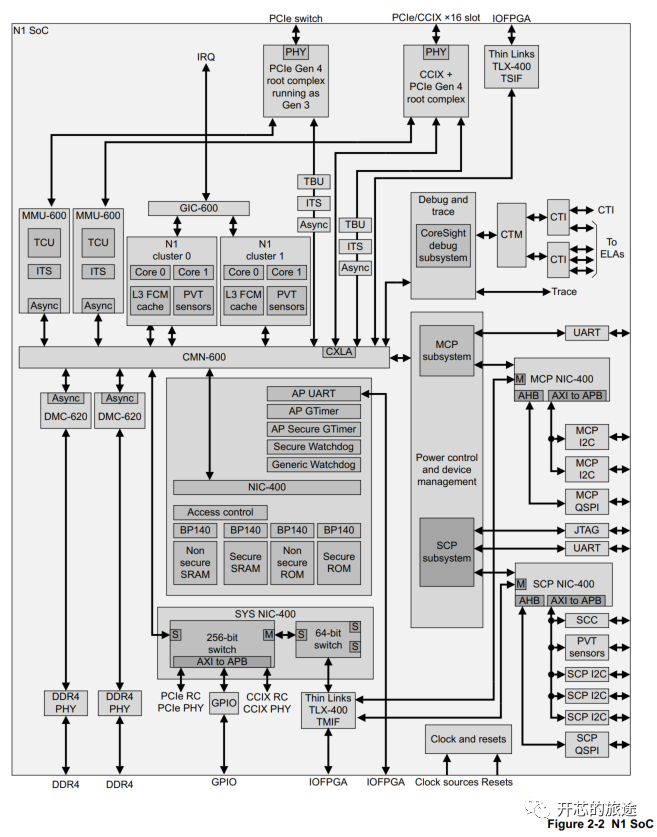

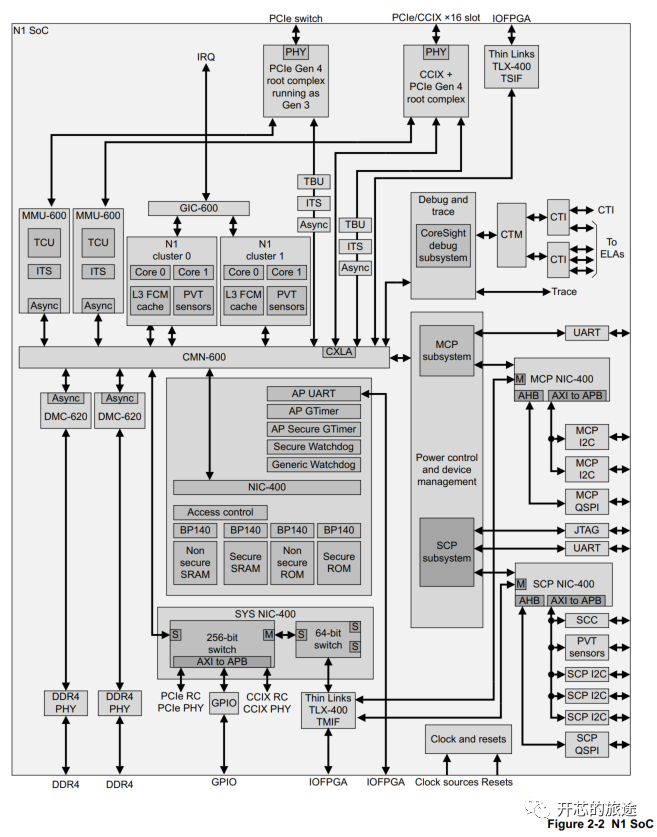

除了提供上述的大型芯片reference design外,ARM还为Neoverse N1做了一套硬件开发板,用于软件的开发验证。开发板的N1 SOC芯片包含4个Neoverse N1,这4个Neoverse N1是分成2个DSU cluster连接到CMN-600上的,并且配备了1MB L3 cache。SOC架构中除了N1 CPU之外,其他像MMU-600、Debug and trace component的使用也值得关注。

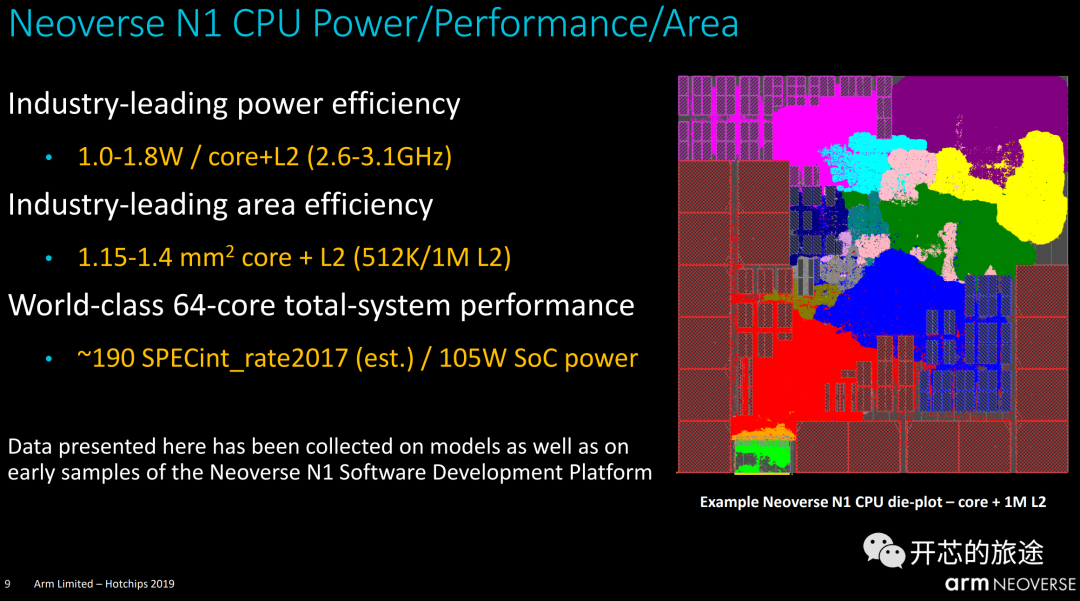

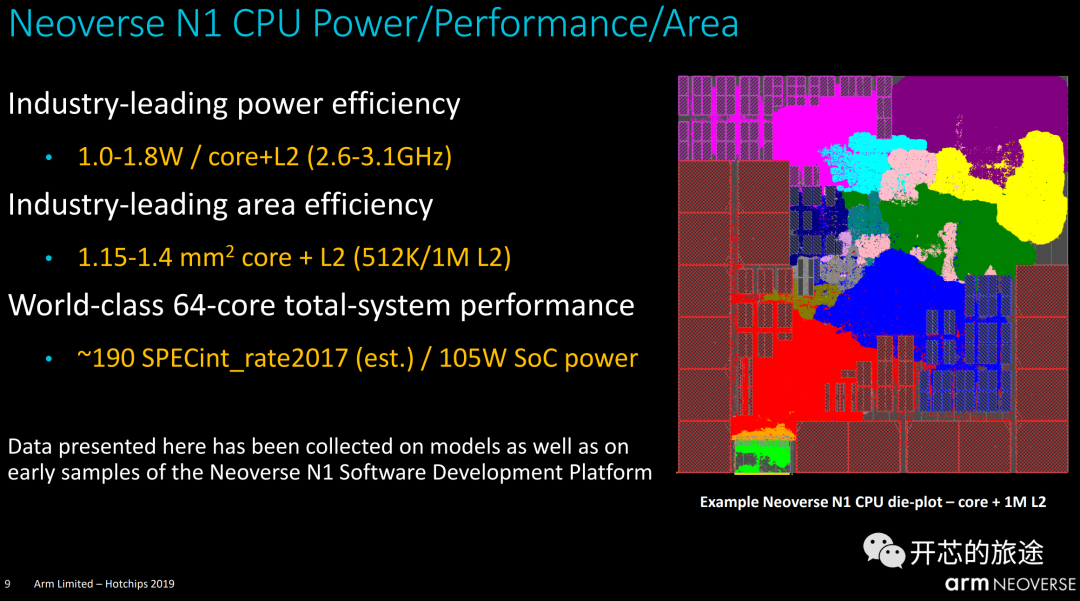

除了提供上述的大型芯片reference design外,ARM还为Neoverse N1做了一套硬件开发板,用于软件的开发验证。开发板的N1 SOC芯片包含4个Neoverse N1,这4个Neoverse N1是分成2个DSU cluster连接到CMN-600上的,并且配备了1MB L3 cache。SOC架构中除了N1 CPU之外,其他像MMU-600、Debug and trace component的使用也值得关注。 (图源:ARM, Arm® Neoverse™ N1 System Development Platform TRM)基于7nm工艺,配置512KB L2的Neoverse N1面积为1.15mm2,配置1MB L2的面积为1.4mm2。整数运算workload(大概率是指dhrystone)的功耗为1.0W @ 2.6GHz和1.8W @ 3.1GHz。

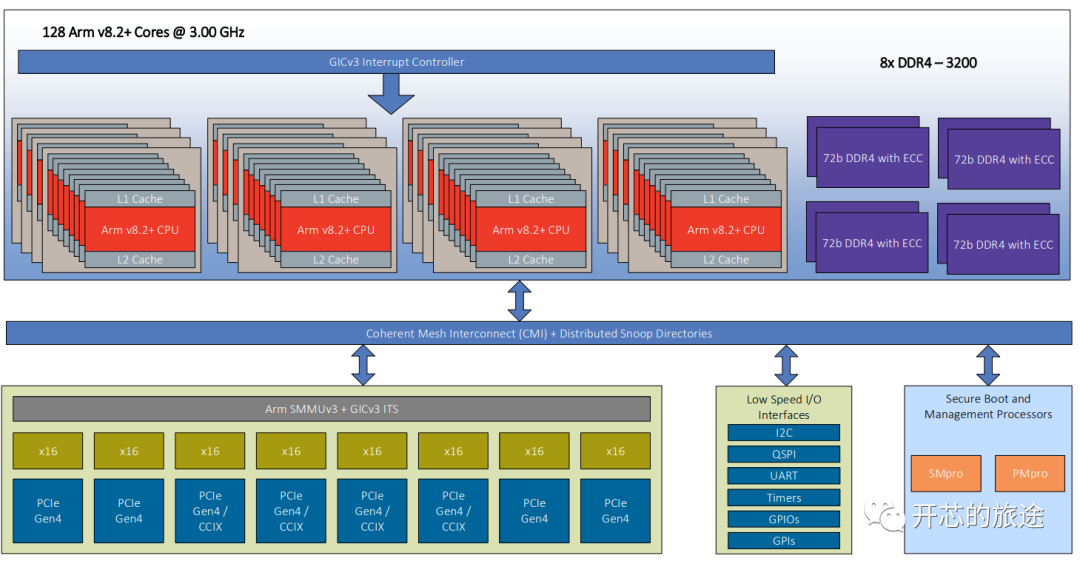

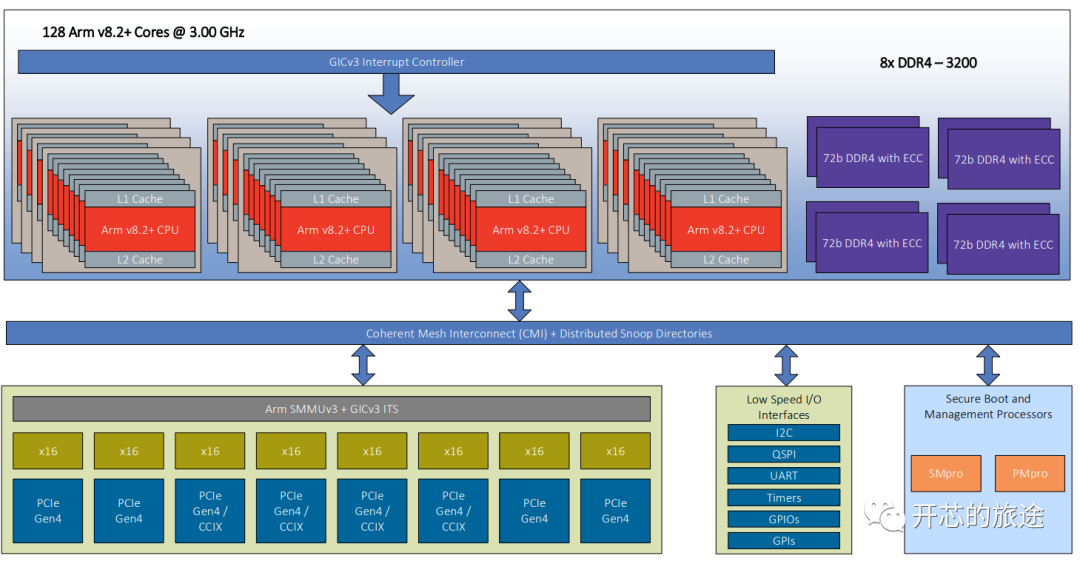

(图源:ARM, Arm® Neoverse™ N1 System Development Platform TRM)基于7nm工艺,配置512KB L2的Neoverse N1面积为1.15mm2,配置1MB L2的面积为1.4mm2。整数运算workload(大概率是指dhrystone)的功耗为1.0W @ 2.6GHz和1.8W @ 3.1GHz。 Ampere Computing,由软银、微软、甲骨文投资,英特尔前总裁Renee James创立的服务器芯片独角兽公司,截至2023年推出3代服务器产品:Ampere Altra:80个Neoverse N1 core,1MB per-core L2,32MB SLC,Max 3.3GHzAmpere Altra Max:128个Neoverse N1 core,1MB per-core L2,16MB SLC,Max 3.0GHz。SPECint2017跑分336分。AmpereOne(2023年5月发布):192个ARM架构自研核下图为128核Neoverse N1的Ampere Altra Max框图:

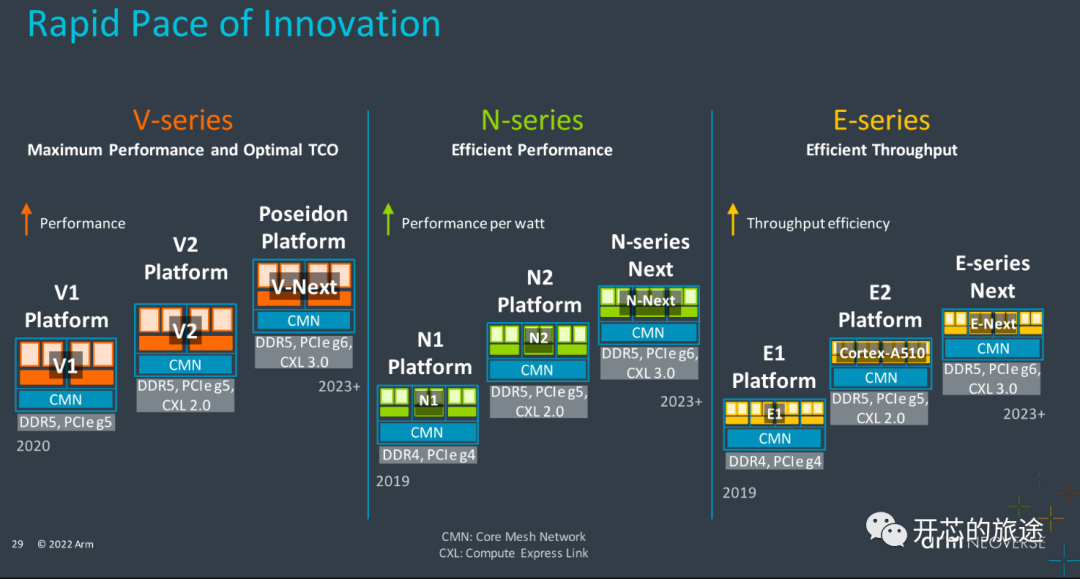

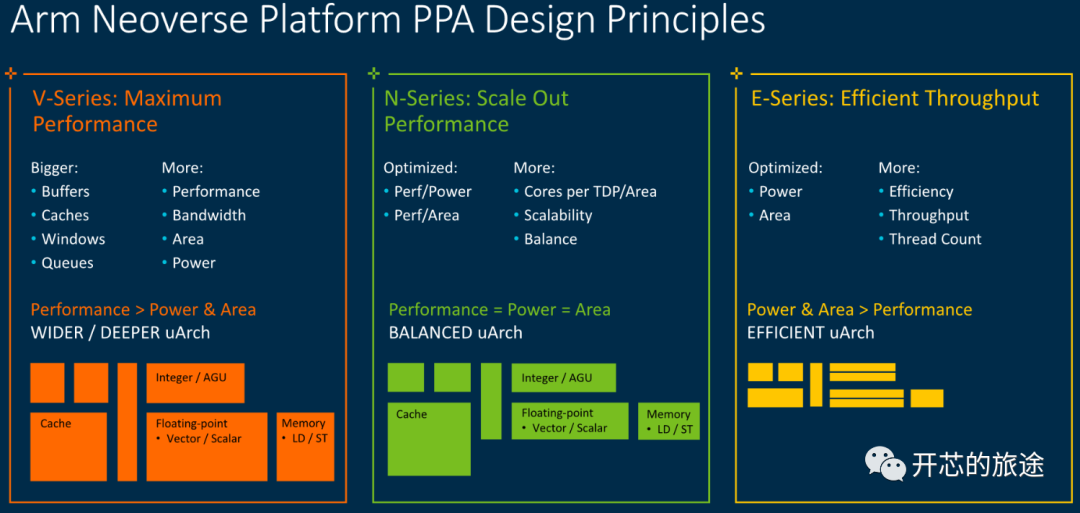

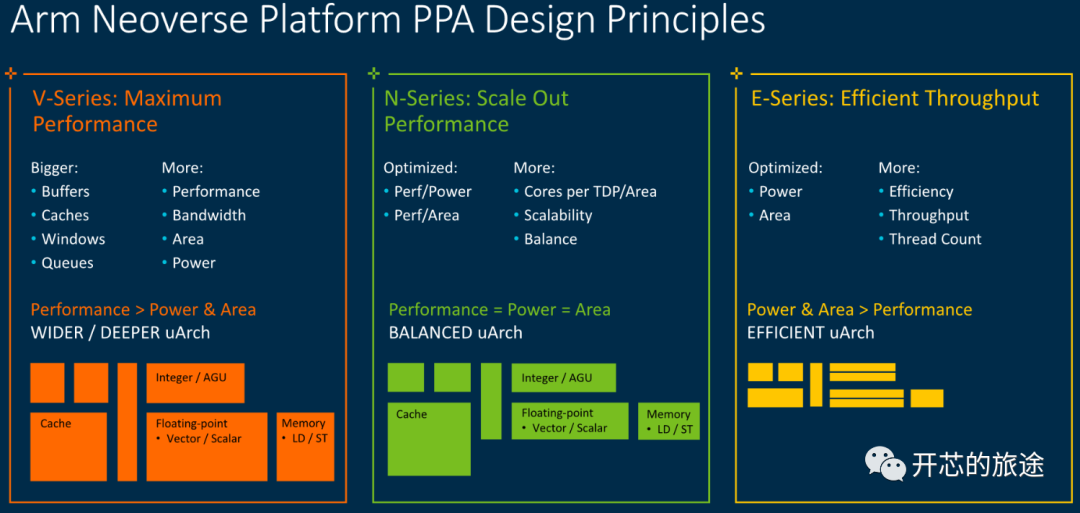

Ampere Computing,由软银、微软、甲骨文投资,英特尔前总裁Renee James创立的服务器芯片独角兽公司,截至2023年推出3代服务器产品:Ampere Altra:80个Neoverse N1 core,1MB per-core L2,32MB SLC,Max 3.3GHzAmpere Altra Max:128个Neoverse N1 core,1MB per-core L2,16MB SLC,Max 3.0GHz。SPECint2017跑分336分。AmpereOne(2023年5月发布):192个ARM架构自研核下图为128核Neoverse N1的Ampere Altra Max框图: (图源:Ampere, Ampere® Altra® Max 64-Bit Multi-Core Processor Datasheet)ARM移动端的Cortex-A系列CPU分为超大核Cortex-X系列,大核Cortex-A7x系列以及小核Cortex-A5x系列。相应地,Neoverse服务器的产品线也分为追求极致性能的V-Series、追求性能与功耗平衡的N-Series以及追求功耗面积的E-Series。

(图源:Ampere, Ampere® Altra® Max 64-Bit Multi-Core Processor Datasheet)ARM移动端的Cortex-A系列CPU分为超大核Cortex-X系列,大核Cortex-A7x系列以及小核Cortex-A5x系列。相应地,Neoverse服务器的产品线也分为追求极致性能的V-Series、追求性能与功耗平衡的N-Series以及追求功耗面积的E-Series。 ARM在2020年9月发布的Neoverse V1,对应移动端的Cortex-X1。

ARM在2020年9月发布的Neoverse V1,对应移动端的Cortex-X1。

根据ARM的PPT,Neoverse V1相比Neoverse N1会有50%的单核性能提升。

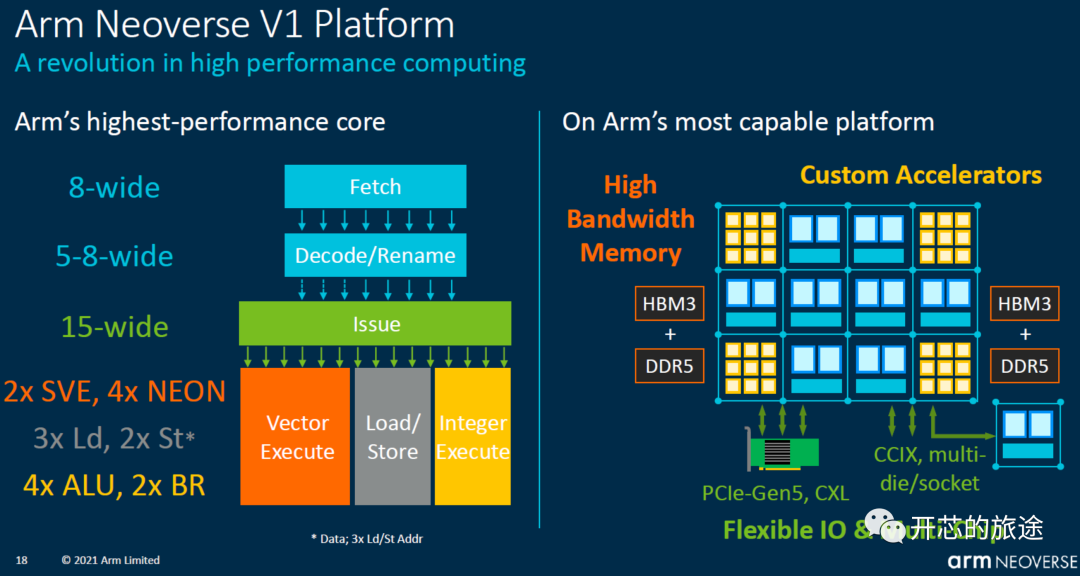

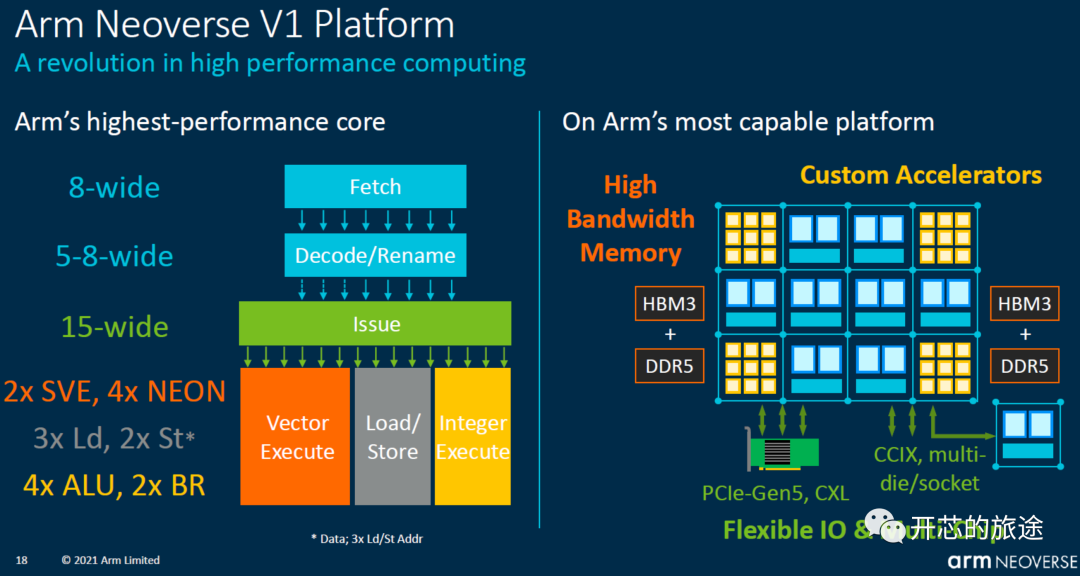

根据ARM的PPT,Neoverse V1相比Neoverse N1会有50%的单核性能提升。 由下图可见,Neoverse V1的取值、译码、发射单元宽度都显著高于N1,ALU等

由下图可见,Neoverse V1的取值、译码、发射单元宽度都显著高于N1,ALU等

但根据2022年底的新闻,由于Neoverse V系列CPU性能太高,受美国和英国的出口管制,中国企业无法购买ARM Neoverse V系列的CPU,包括Neoverse V1以及后续的Neoverse V2等。

但根据2022年底的新闻,由于Neoverse V系列CPU性能太高,受美国和英国的出口管制,中国企业无法购买ARM Neoverse V系列的CPU,包括Neoverse V1以及后续的Neoverse V2等。

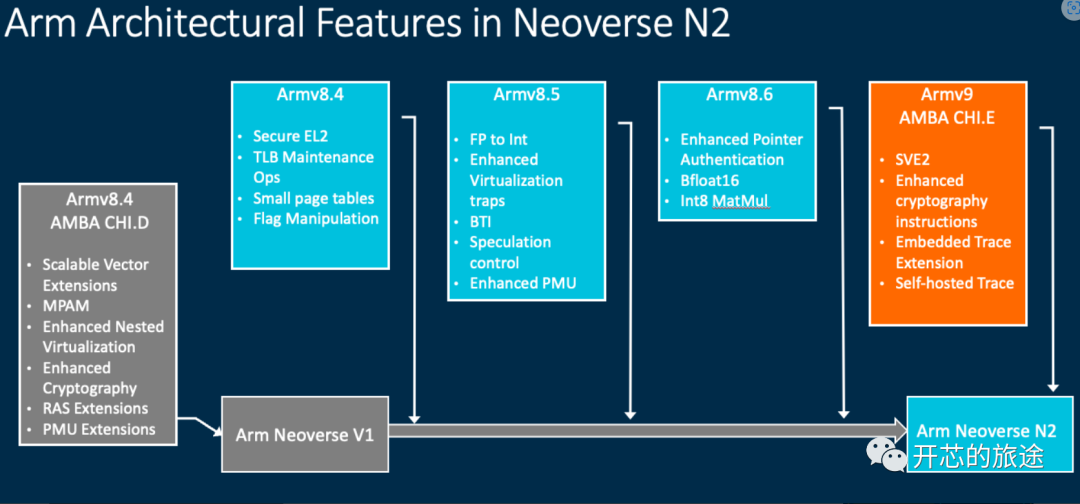

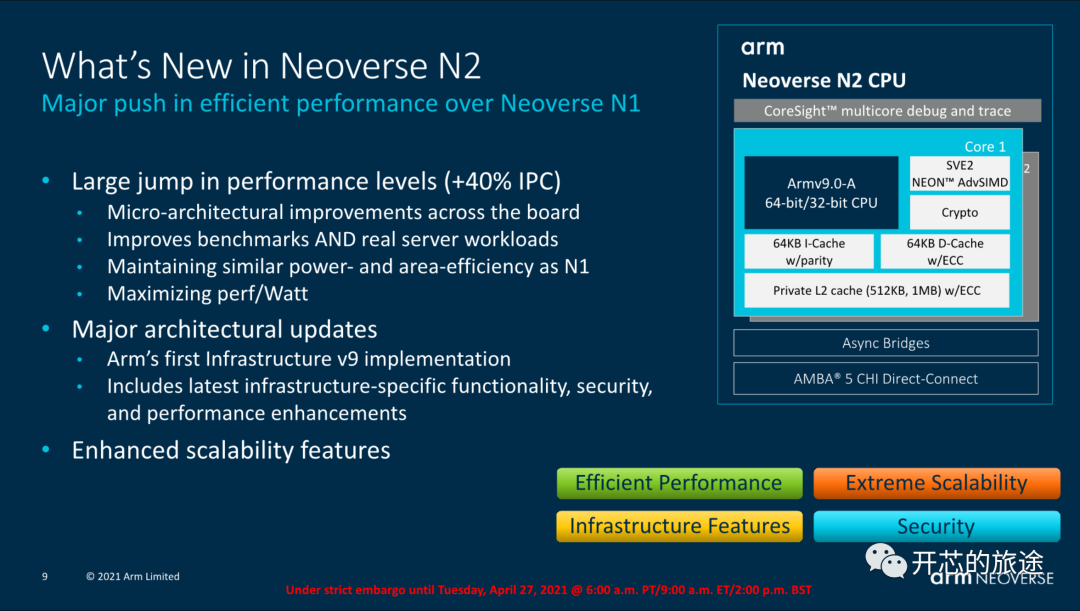

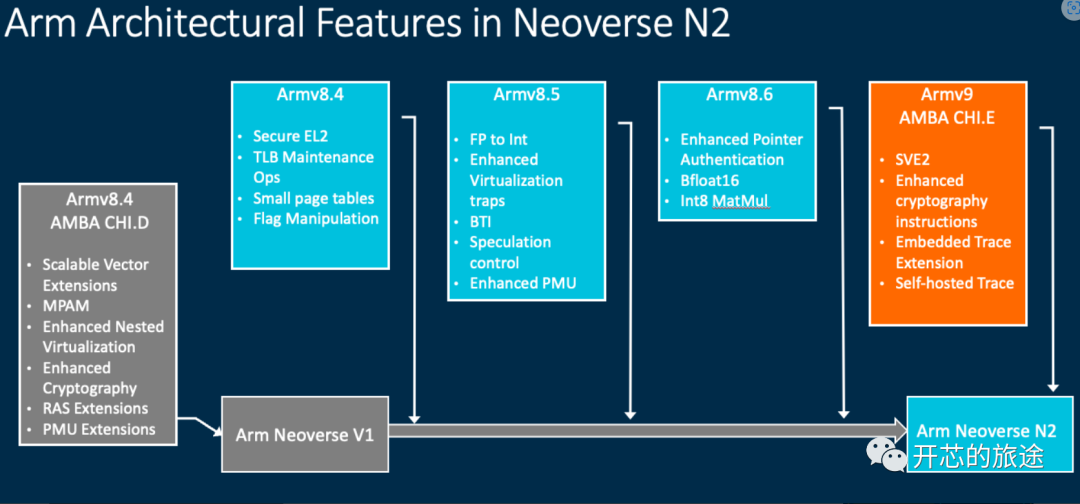

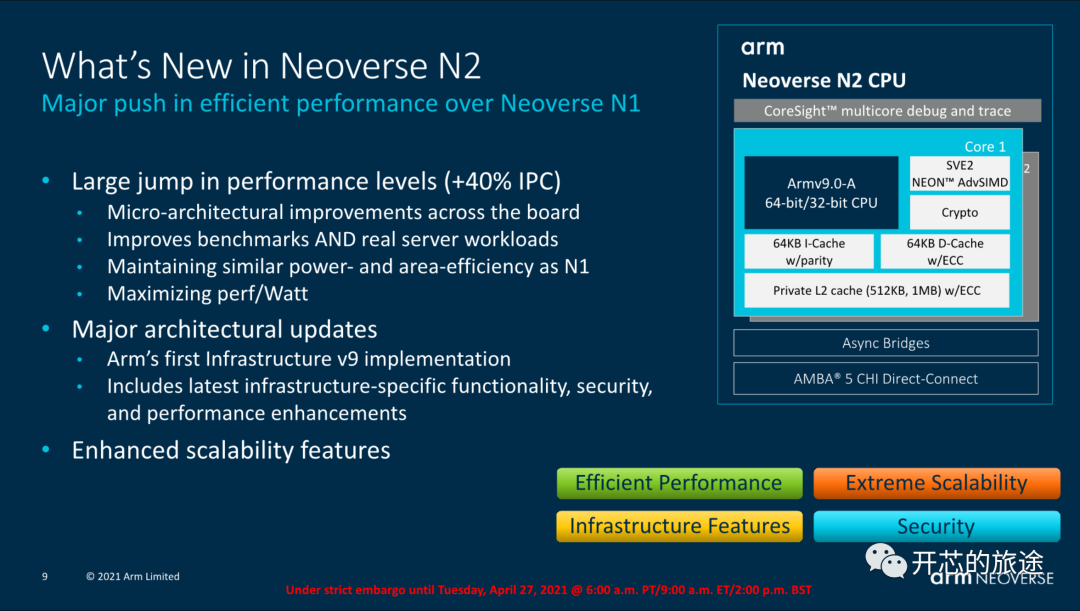

Neoverse N2是ARM首款ARMv9系列的服务器CPU。与移动端的Cortex-A710是同一代的CPU。相比Neoverse V1,增加了SVE2、Memory Tagging Extension(MTE)等ARMv9一代CPU的新feature。

(图源:ARM,Arm Neoverse N2 Platform: Industry-leading performance and power efficiency for Cloud-to-Edge infrastructure)根据ARM的PPT,Neoverse N2相比N1有40%的IPC提升:

(图源:ARM,Arm Neoverse N2 Platform: Industry-leading performance and power efficiency for Cloud-to-Edge infrastructure)根据ARM的PPT,Neoverse N2相比N1有40%的IPC提升:

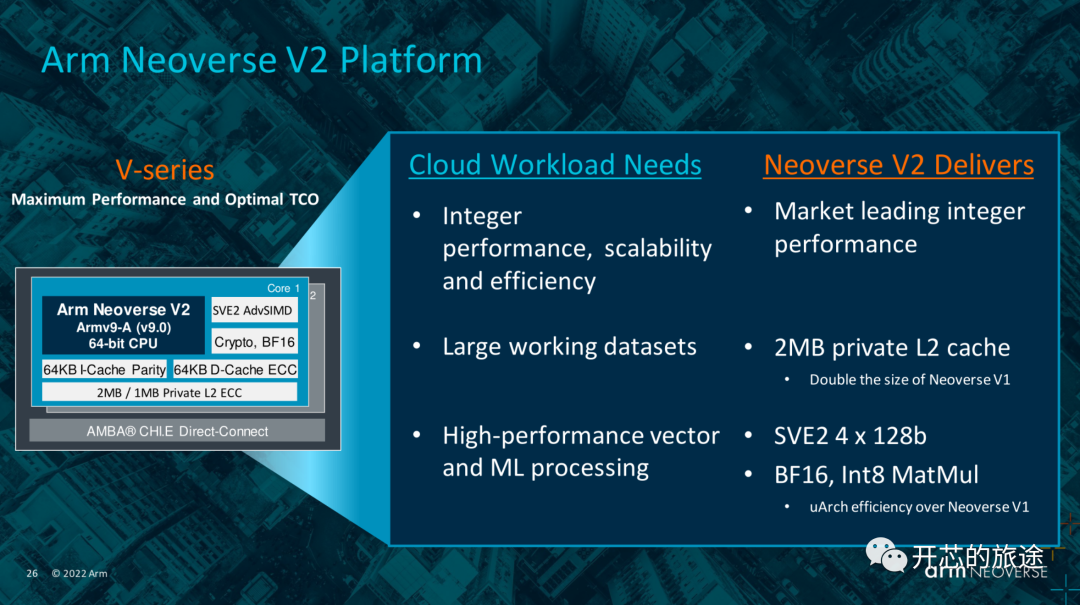

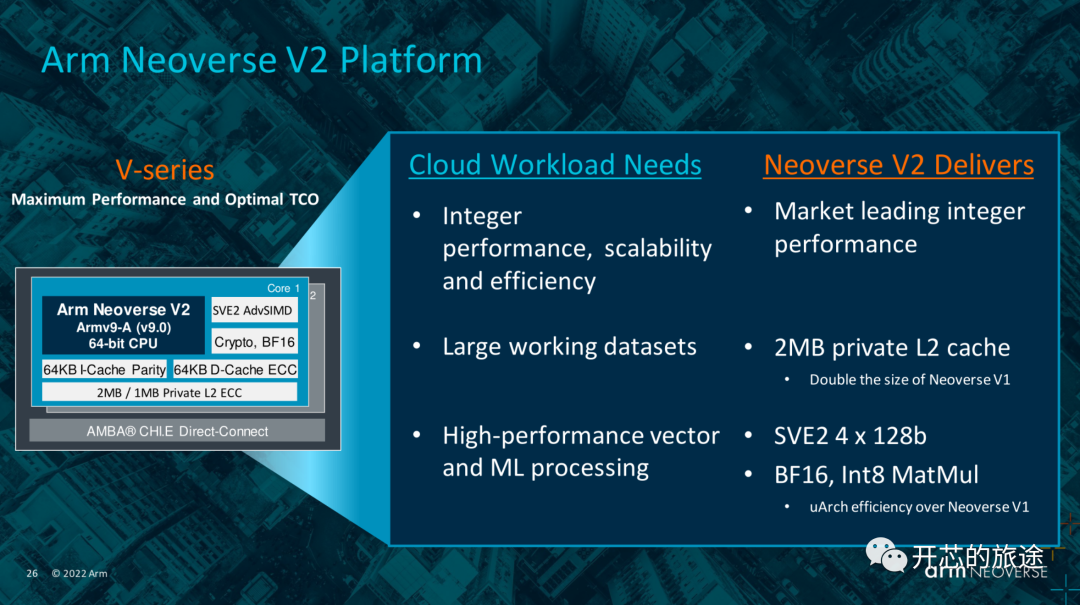

2021年10月,平头哥发布倚天710,基于TSMC 5nm工艺,采用128核的Neoverse N2,最高频率3.2GHz,8通道DDR5,峰值总带宽281GB/s,96通道PCIe 5.0。SPECInt 2017跑分440分。倚天710分为两个die,每个die包含64个CPU core和4个通道的DDR。根据网上信息,每个die size约310mm2。倚天710采用2.5D封装进行多die合封,总计600亿晶体管。所使用的总线大概率是与Neoverse N2同一时期的CMN-700,每个die上有一个CMN总线。ARM于2022年9月发布Neoverse V2 CPU。相比Neoverse V1,所支持的最大L2 cache size从1MB提升到2MB。另外支持ARM v9.0的新feature,如SVE2 4x128b。

2021年10月,平头哥发布倚天710,基于TSMC 5nm工艺,采用128核的Neoverse N2,最高频率3.2GHz,8通道DDR5,峰值总带宽281GB/s,96通道PCIe 5.0。SPECInt 2017跑分440分。倚天710分为两个die,每个die包含64个CPU core和4个通道的DDR。根据网上信息,每个die size约310mm2。倚天710采用2.5D封装进行多die合封,总计600亿晶体管。所使用的总线大概率是与Neoverse N2同一时期的CMN-700,每个die上有一个CMN总线。ARM于2022年9月发布Neoverse V2 CPU。相比Neoverse V1,所支持的最大L2 cache size从1MB提升到2MB。另外支持ARM v9.0的新feature,如SVE2 4x128b。

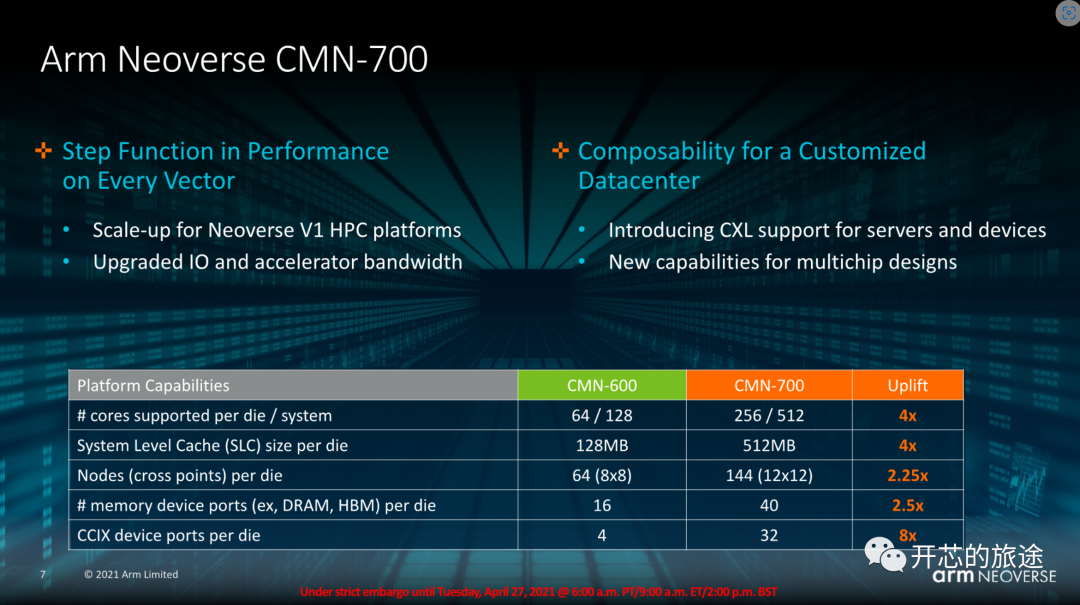

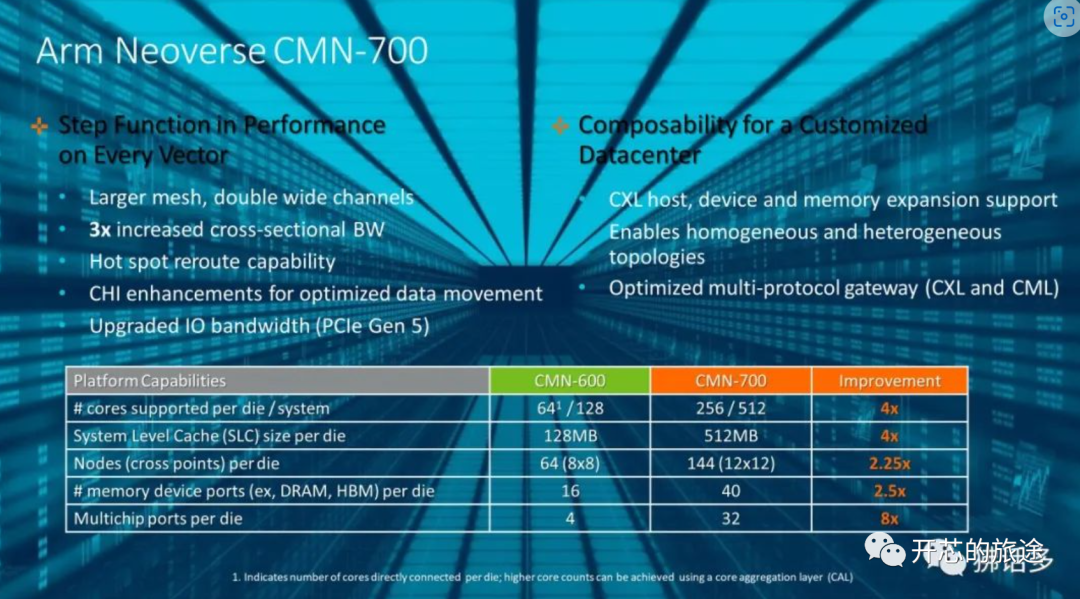

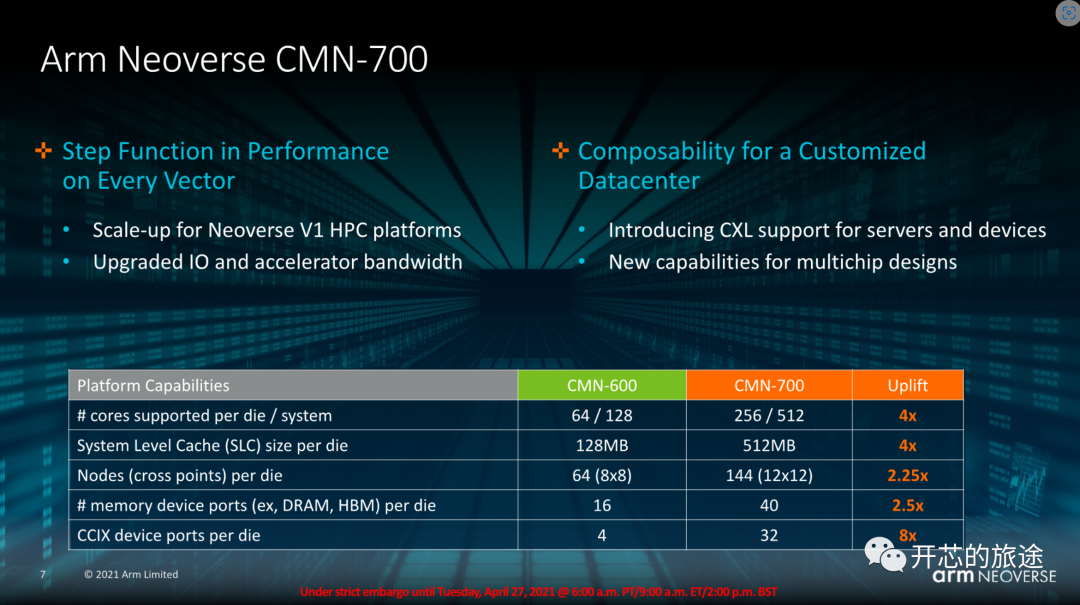

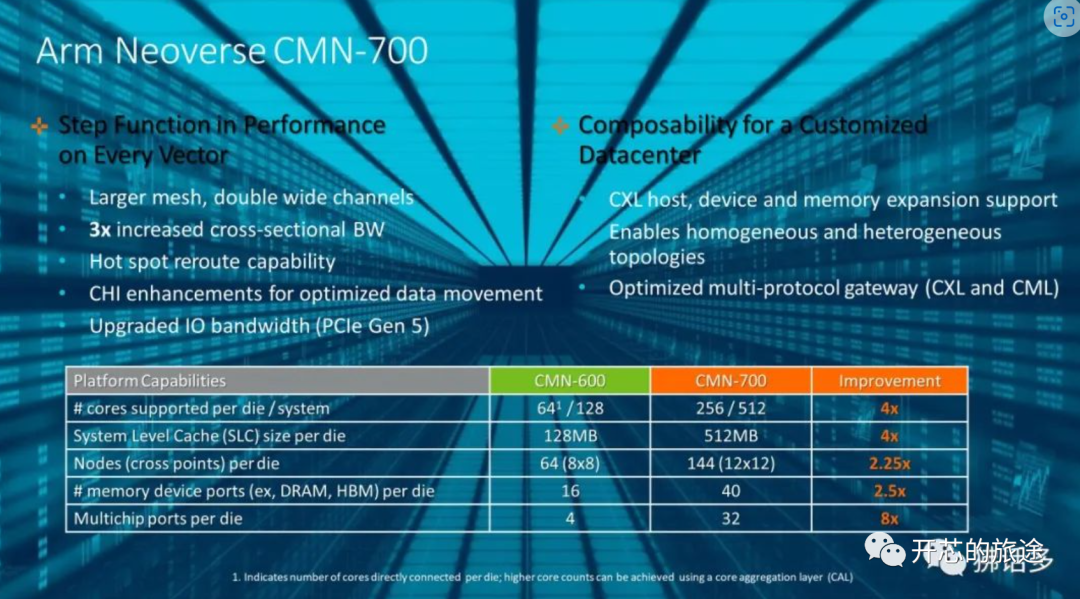

除了ARM Neoverse系列CPU之外,CMN总线也是ARM服务器架构中的重要组件。CMN-700相比CMN-600提升了每个die上支持的core数量、mesh的Node数量以及System level cache的容量等。

除了ARM Neoverse系列CPU之外,CMN总线也是ARM服务器架构中的重要组件。CMN-700相比CMN-600提升了每个die上支持的core数量、mesh的Node数量以及System level cache的容量等。

其中CMN-700所支持的256 cores per die是这样计算的,CMN-700可以支持128个RN-F(Full coherent的Requesting Node),每个RN-F可以是两个Neoverse CPU core经过CMN-700的CAL(Component Aggregation Layer)组件汇聚成一路。所以总共支持128 * 2 = 256 cores。

其中CMN-700所支持的256 cores per die是这样计算的,CMN-700可以支持128个RN-F(Full coherent的Requesting Node),每个RN-F可以是两个Neoverse CPU core经过CMN-700的CAL(Component Aggregation Layer)组件汇聚成一路。所以总共支持128 * 2 = 256 cores。

理论上来说,CMN-600可以支持64个RN-F,所以理论上能够支持的core数量应该也能到64 * 2 = 128 cores(实际上会略小于这个值)。因为Ampere Altra这一代服务器芯片就已经有80个Neoverse N1 core,超出了ARM给出的64 core per die。ARM给出的说法是这个64 core per die是指直连到Node上的core数量,如果采用CAL的话,可以实现更高的core数量。请留意下图中最下面一行小字: 如果要实现128 core的服务器芯片,可以选择在一个die上使用CMN-700来构建,也可以通过多die互联,例如下图左侧就是2个64 core的die进行die间互联。采用64 core per die,用两个die组成128 core服务器芯片的方式,每个die的size比较小,良率会更高,代价是需要有额外的逻辑实现片间互联。

如果要实现128 core的服务器芯片,可以选择在一个die上使用CMN-700来构建,也可以通过多die互联,例如下图左侧就是2个64 core的die进行die间互联。采用64 core per die,用两个die组成128 core服务器芯片的方式,每个die的size比较小,良率会更高,代价是需要有额外的逻辑实现片间互联。