GPU巨头,拼什么?

来源:半导体行业观察 发布时间:2023-07-14 12:39:54 阅读量:884

在 GPU 领域,2022 年无论好坏都是一个重要的里程碑。英特尔兑现了重新进入独立显卡市场的承诺,Nvidia将显卡尺寸和价格推向了顶峰,AMD将 CPU 技术带入了显卡领域。

围绕 GPU 的热情弥漫在在线论坛中,让 PC 爱好者对显卡市场的转变感到既敬畏又震惊。在这种喧嚣中,人们很容易忘记最新的产品配备了家用电脑中最复杂、最强大的芯片。

在本文中,我们将深入探讨他们的架构。让我们剥开层层,看看有什么新内容、它们有什么共同点,以及这些对普通用户意味着什么。

GPU整体结构:从上到下

让我们从本文的一个重要方面开始——这不是性能比较。相反,我们正在研究 GPU 内部的所有内容是如何排列的,检查规格和数据,以了解 AMD、英特尔和 Nvidia 在设计图形处理器时所采用的方法差异。

我们将首先了解使用我们正在研究的架构的最大可用芯片的整体 GPU 组成。需要强调的是,英特尔的产品并不针对与 AMD 或 Nvidia 相同的市场,因为它在很大程度上是一款中档图形处理器。

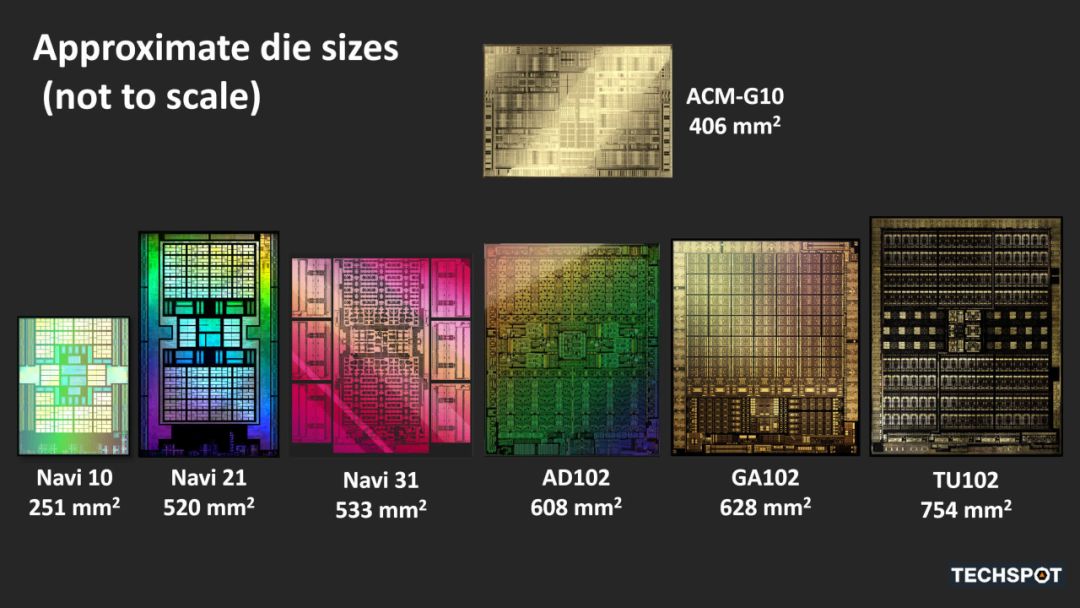

这三者的尺寸不仅彼此不同,而且与使用先前架构的类似芯片也有很大不同。所有这些分析纯粹是为了了解这三个处理器的底层到底是什么。在分解每个 GPU 的基本部分(着色器核心、光线追踪功能、内存层次结构以及显示和媒体引擎)之前,我们将检查整体结构。

一、AMD Navi 31

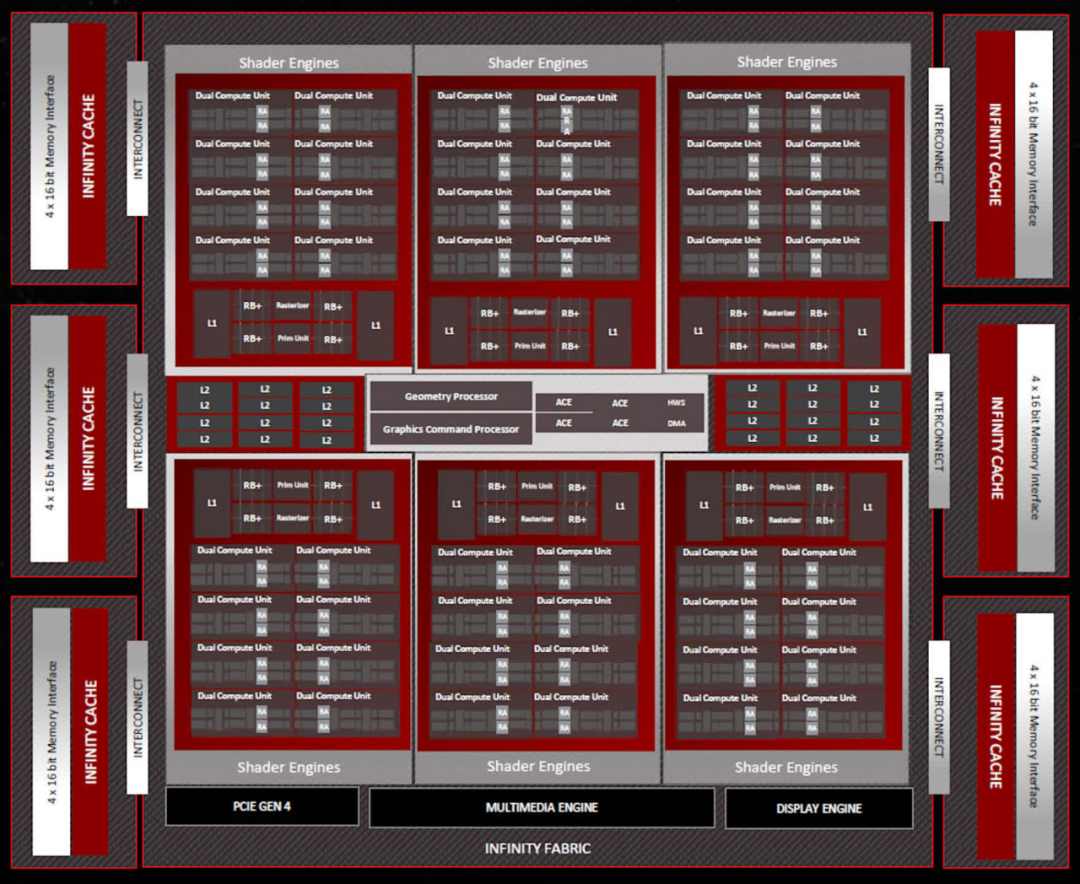

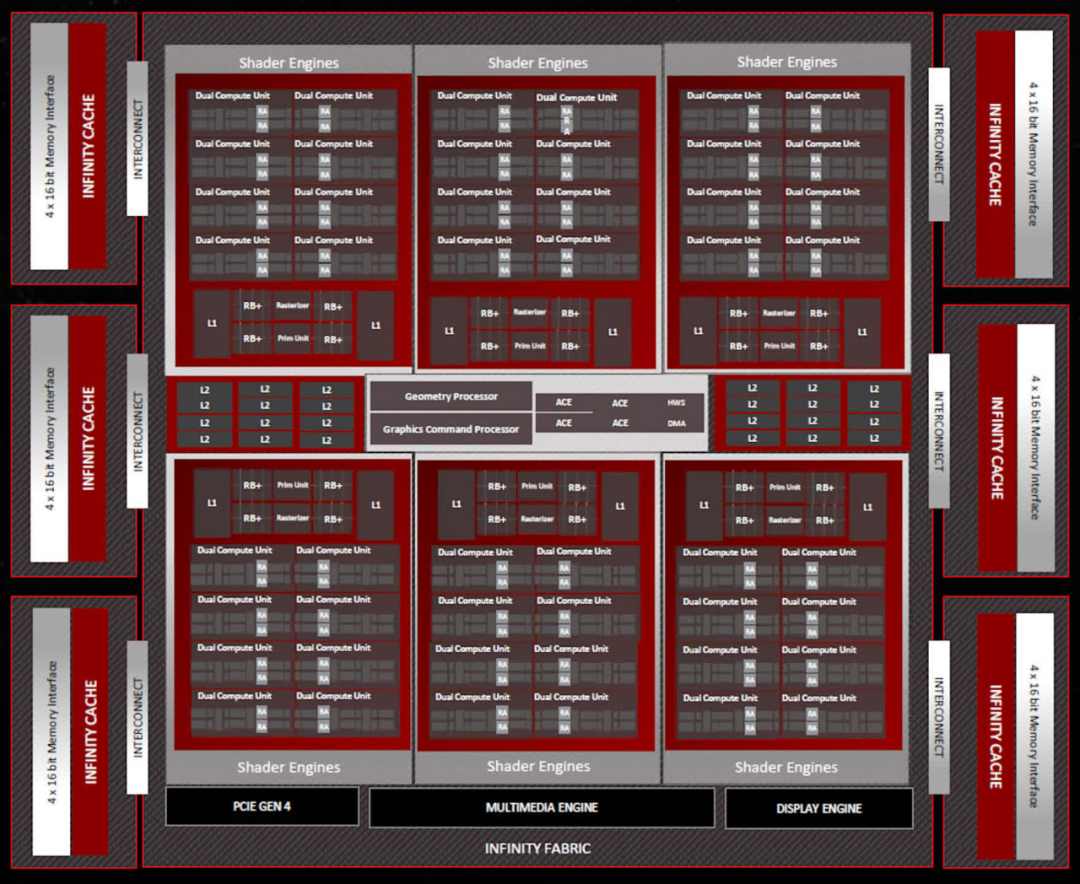

按字母顺序排列,第一个出现的是 AMD 的 Navi 31,这是他们迄今为止发布的最大的 RDNA 3 芯片。与 Navi 21 相比,我们可以看到他们之前的高端 GPU 的组件数量明显增长......

着色器引擎 (SE:Shader Engines) 容纳的计算单元 (CU:Compute Units) 较少,为 16 个,而不是 200 个,但现在总共有 6 个 SE,比以前多了两个。这意味着Navi 31拥有多达96个CU,总共配备6144个流处理器(SP:Stream Processors)。AMD 已经对 RDNA 3 的 SP 进行了全面升级,我们将在后面讨论。

每个着色器引擎还包含一个处理光栅化( rasterization)的专用单元、一个用于三角形( triangle )设置的图元引擎(primitive engine )、32 个渲染输出单元 (ROP:render output units) 和两个 256kB L1 缓存。最后一个方面现在大小增加了一倍,但每个 SE 的 ROP 计数仍然相同。

AMD 也没有对光栅器( rasterizer )和原始引擎(primitive engines)进行太大改变——所称的 50% 改进是针对整个芯片进行的,因为它的 SE 比 Navi 21 芯片多了 50%。然而,SE 处理指令的方式发生了变化,例如更快地处理多个绘制命令(multiple draw commands)和更好地管理管道阶段( pipeline stages),这应该会减少 CU 在继续执行另一个任务之前需要等待的时间。

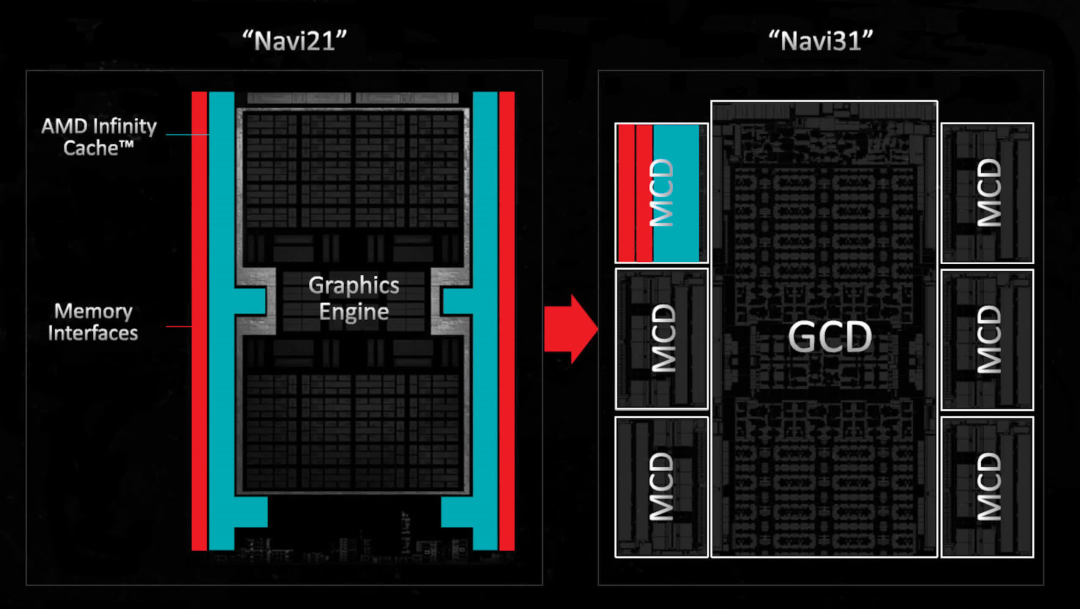

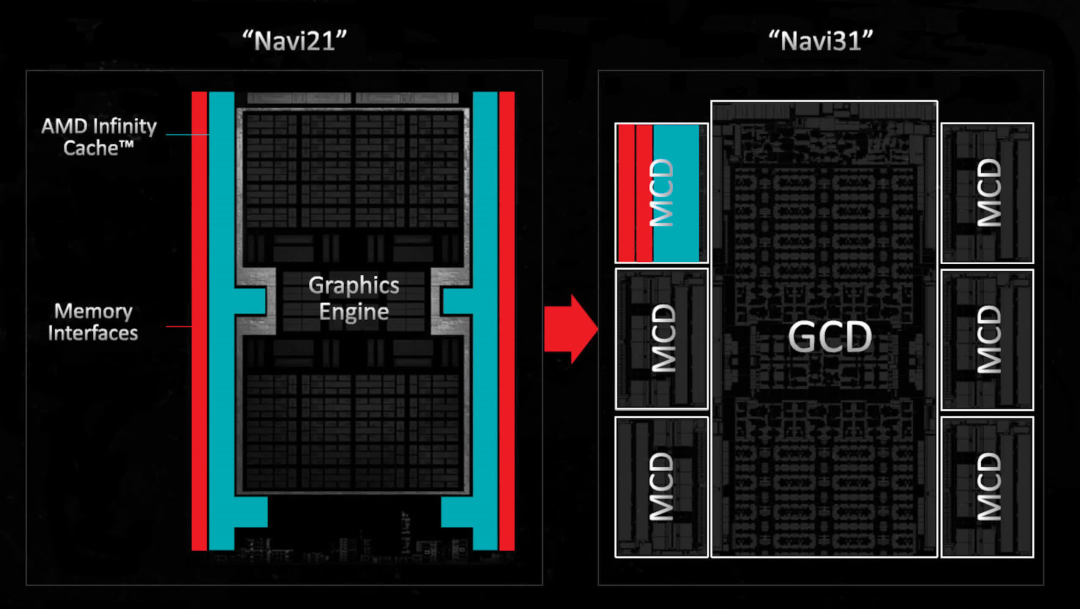

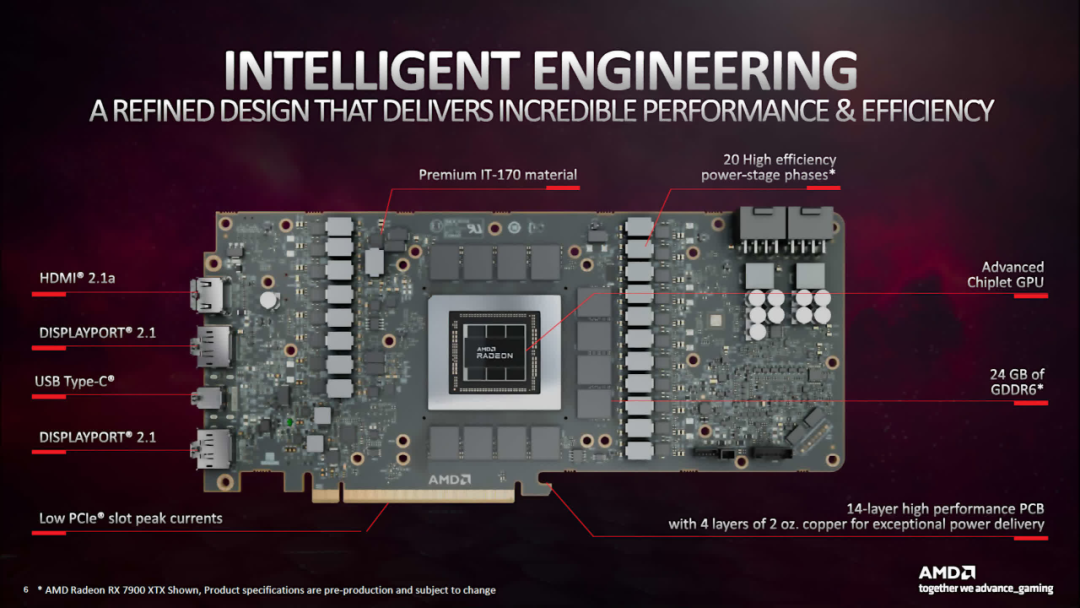

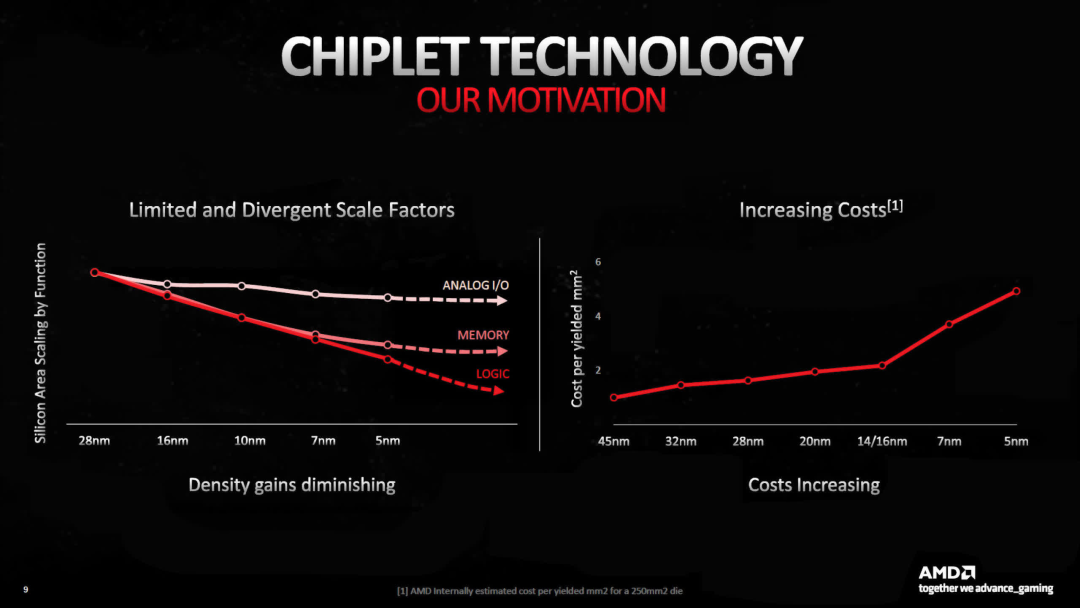

最明显的变化是在 11 月发布之前引起最多谣言和八卦的变化——GPU 封装的小芯片方法。凭借在该领域多年的经验,AMD 选择这样做在某种程度上是合乎逻辑的,但这完全是出于成本/制造原因,而不是性能。

我们将在本文后面更详细地讨论这一点,所以现在我们只关注哪些部分在哪里。在 Navi 31 中,最终层缓存的内存控制器及其相关分区位于主处理器(GCD,Graphics Compute Die)周围的单独小芯片(称为 MCD 或Memory Cache Dies)中。

由于需要提供更多数量的 SE,AMD 也将 MC 数量增加了 50%,因此 GDDR6 全局内存的总总线宽度现在为 384 位。这次 Infinity Cache 总量减少了(96MB vs 128MB),但更大的内存带宽抵消了这一点。

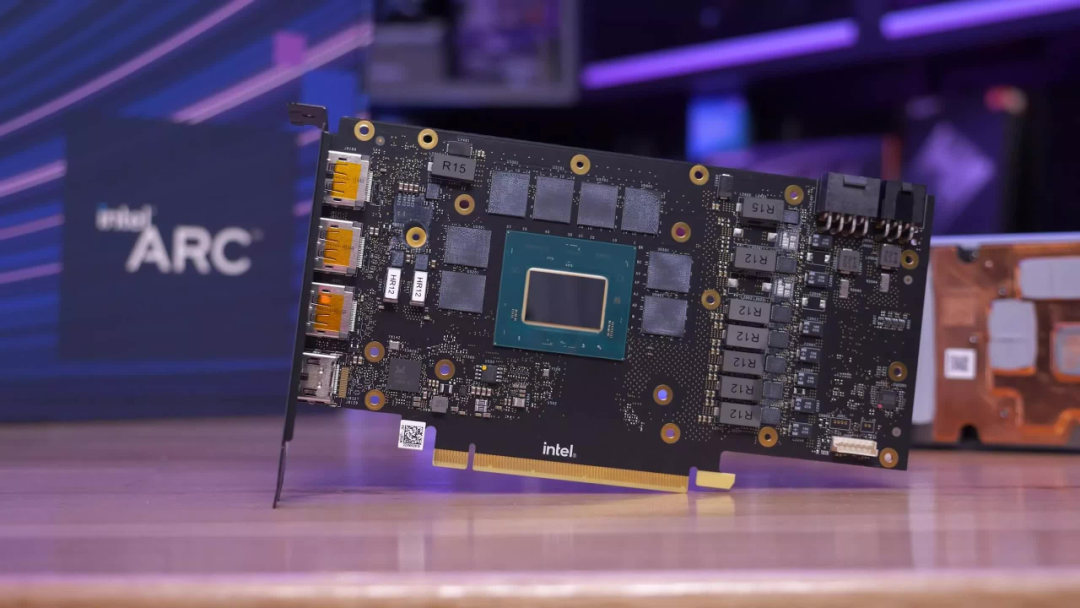

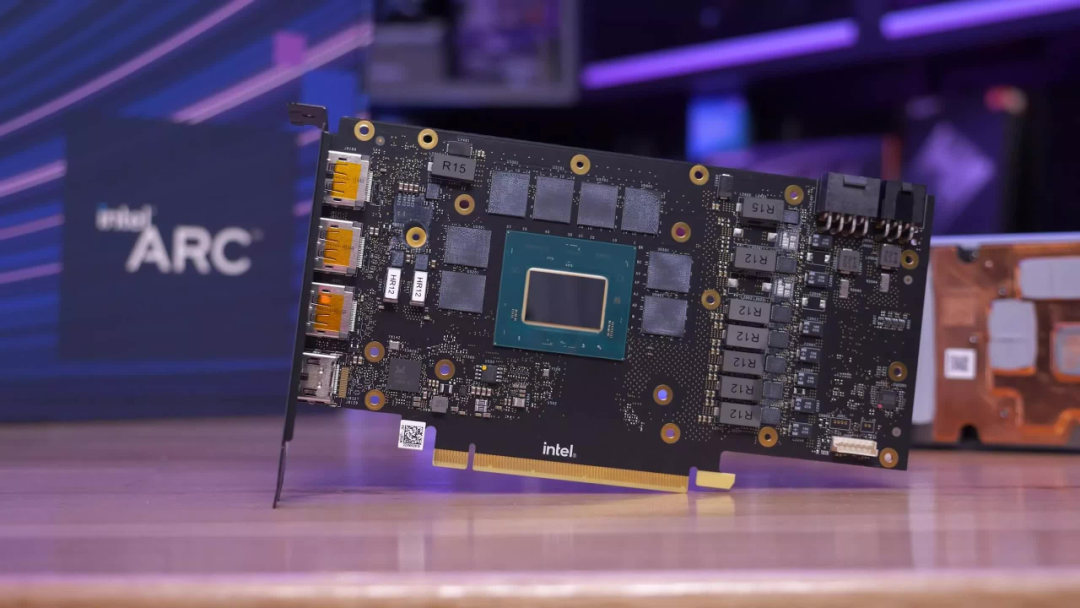

二、英特尔ACM-G10

接下来是 Intel 和 ACM-G10 芯片(以前称为 DG2-512)。虽然这不是英特尔生产的最大的 GPU,但它是他们最大的消费类图形芯片。

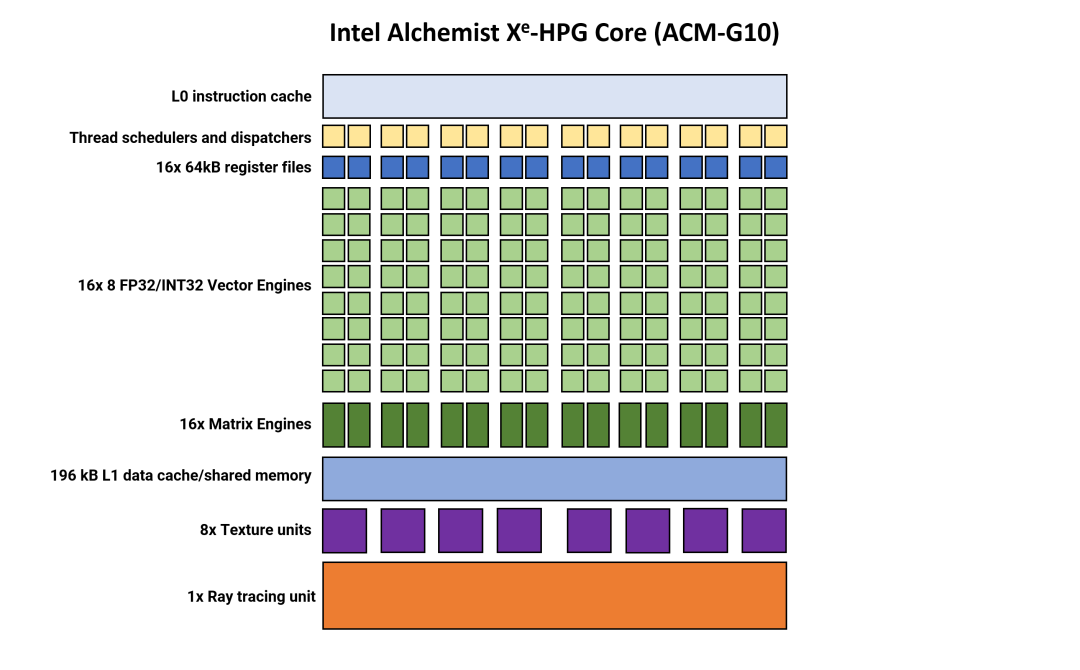

该框图是相当标准的排列,尽管看起来更类似于 Nvidia 的而不是 AMD 的。共有 8 个渲染切片(Render Slices),每个渲染切片包含 4 个 Xe 核心,总共 512 个矢量引擎(Vector Engines:相当于 AMD 的流处理器和 Nvidia 的 CUDA 核心 )。

每个渲染切片中还包含一个基元单元、光栅器、深度缓冲处理器、32 个纹理单元和 16 个 ROP。乍一看,这款 GPU 似乎相当大,因为 256 个 TMU 和 128 个 ROP 比 Radeon RX 6800 或 GeForce RTX 2080 中的数量还要多。

然而,AMD 的 RNDA 3 芯片拥有 96 个计算单元,每个计算单元有 128 个 ALU,而 ACM-G10 总共有 32 个 Xe 核心,每个核心有 128 个 ALU。因此,仅就 ALU 数量而言,英特尔 Alchemist 驱动的 GPU 的大小是 AMD 的三分之一。但正如我们稍后将看到的,ACM-G10 的大部分芯片都交给了不同的数字处理单元。

与英特尔通过 OEM 供应商发布的首款 Alchemist GPU相比,该芯片在组件数量和结构排列方面具备成熟架构的所有特征。

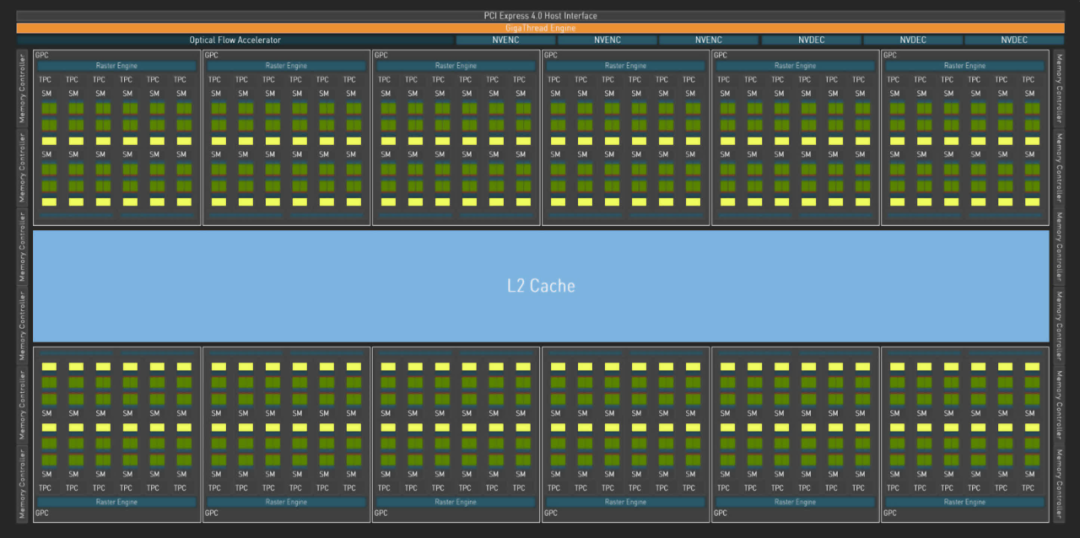

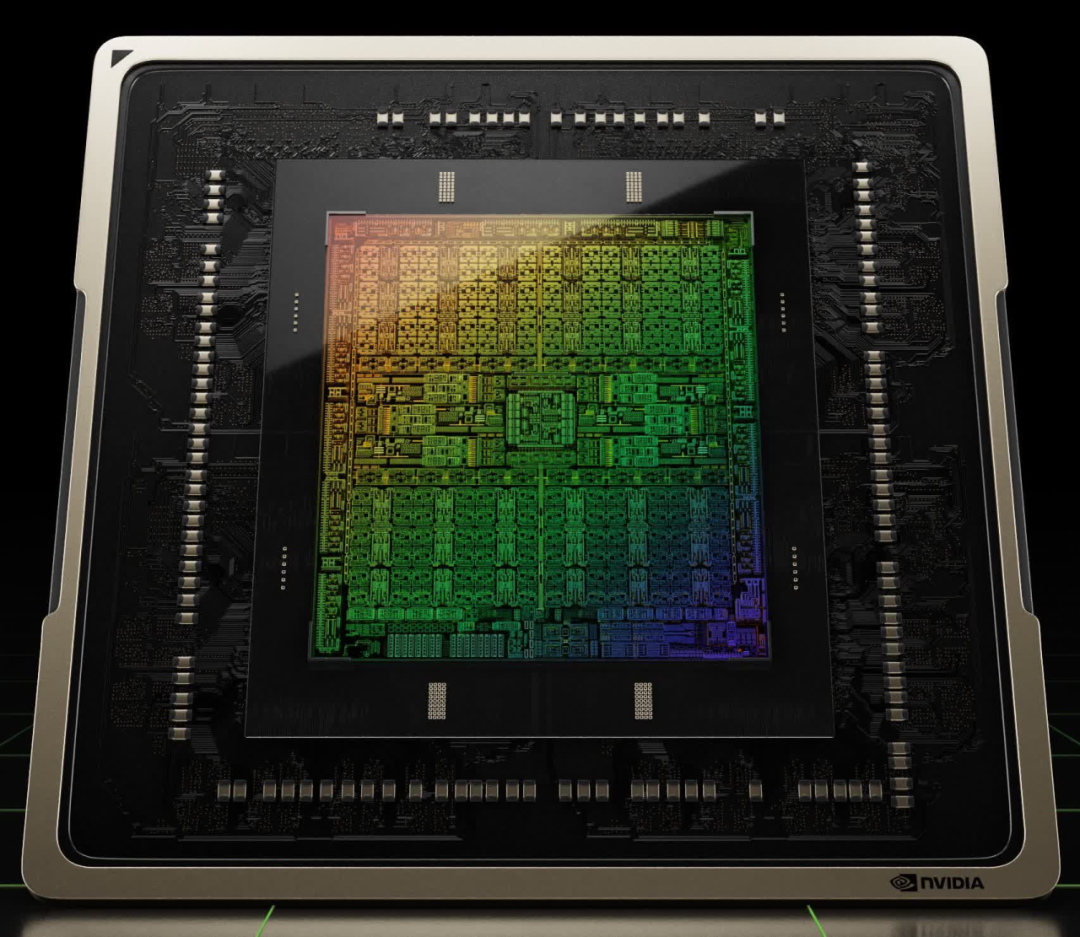

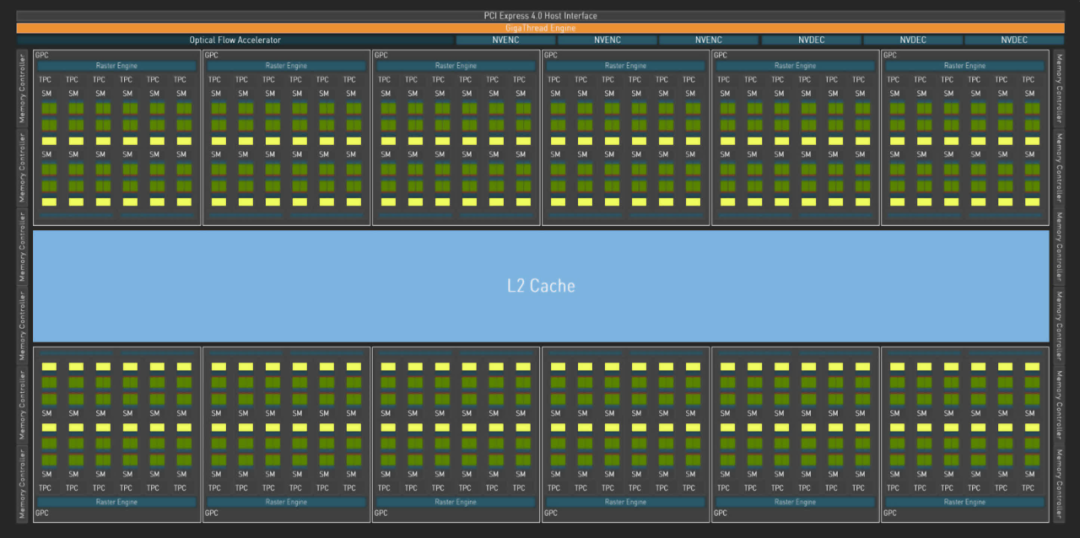

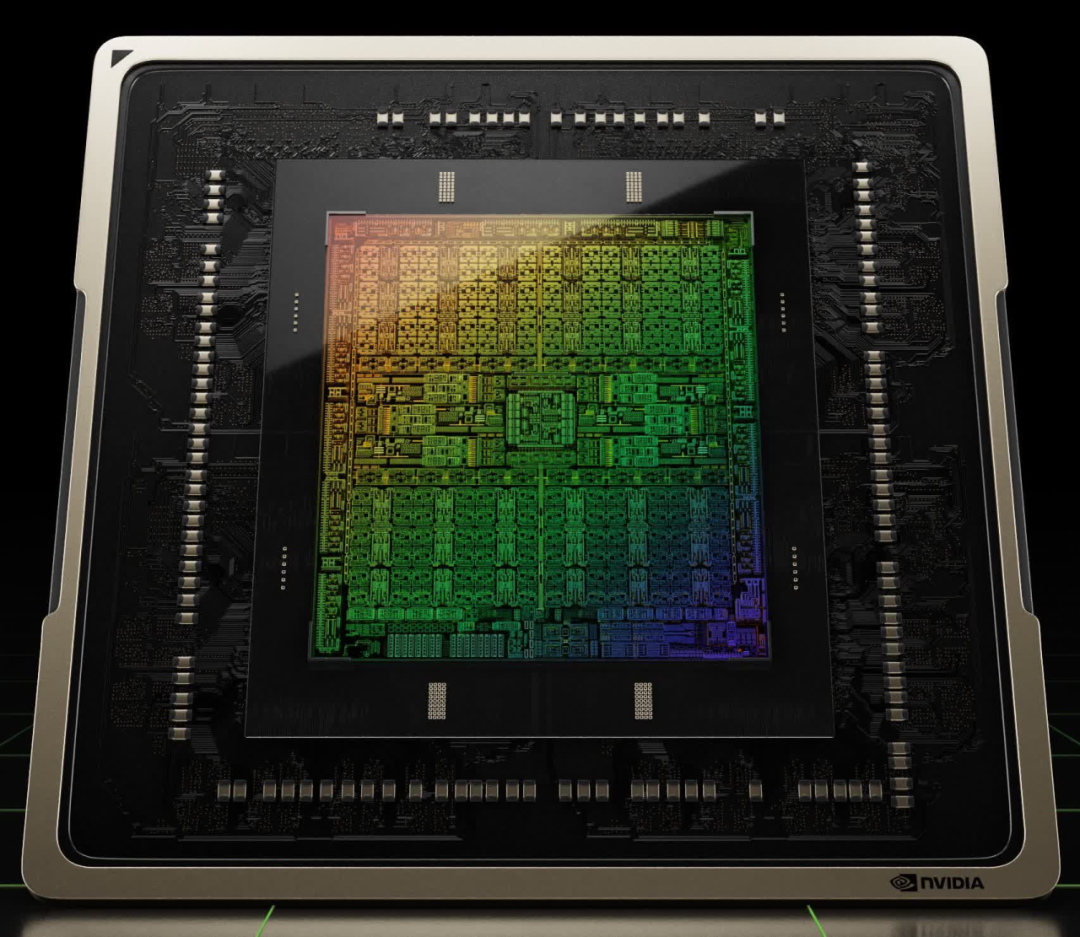

三、英伟达AD102

我们完成了对 Nvidia AD102 不同布局的开场概述,这是他们第一个使用 Ada Lovelace 架构的 GPU。与它的前身Ampere GA102相比,它看起来并没有什么不同,只是大了很多。就所有意图和目的而言,确实如此。

Nvidia 使用图形处理集群 (GPU:Graphics Processing Cluster) 的组件层次结构,其中包含 6 个纹理处理集群 (TPC:Texture Processing Clusters),每个集群包含 2 个流式多处理器 (SM)。这种安排对于Ada来说并没有改变,但总数肯定已经改变了……

在完整的 AD102 芯片中,GPC 数量从 7 个增加到 12 个,因此现在总共有 144 个 SM,总共有 18432 个 CUDA 核心。与 Navi 31 中的 6144 个 SP 相比,这个数字似乎高得离谱,但 AMD 和 Nvidia 对其组件的计数方式不同。

虽然这大大简化了问题,但 1 个 Nvidia SM 相当于 1 个 AMD CU——两者都包含 128 个 ALU。因此,Navi 31 的尺寸是英特尔 ACM-G10 的两倍(仅 ALU 数量),而 AD102 的尺寸是英特尔 ACM-G10 的 3.5 倍。

这就是为什么当芯片在规模上有如此明显的差异时,对它们进行任何直接的性能比较是不公平的。然而,一旦它们进入显卡、定价并上市,那么情况就不同了。

但我们可以比较的是三个处理器中最小的重复部分。

着色器核心(Shader Cores):

走进 GPU 的大脑

从整个处理器的概述开始,现在让我们深入了解芯片的核心,看看处理器的基本数字处理部分:着色器核心。

这三个制造商在描述他们的芯片时使用不同的术语和短语,特别是在概述图时。因此,在本文中,我们将使用我们自己的图像,具有常见的颜色和结构,以便更容易看出相同和不同之处。

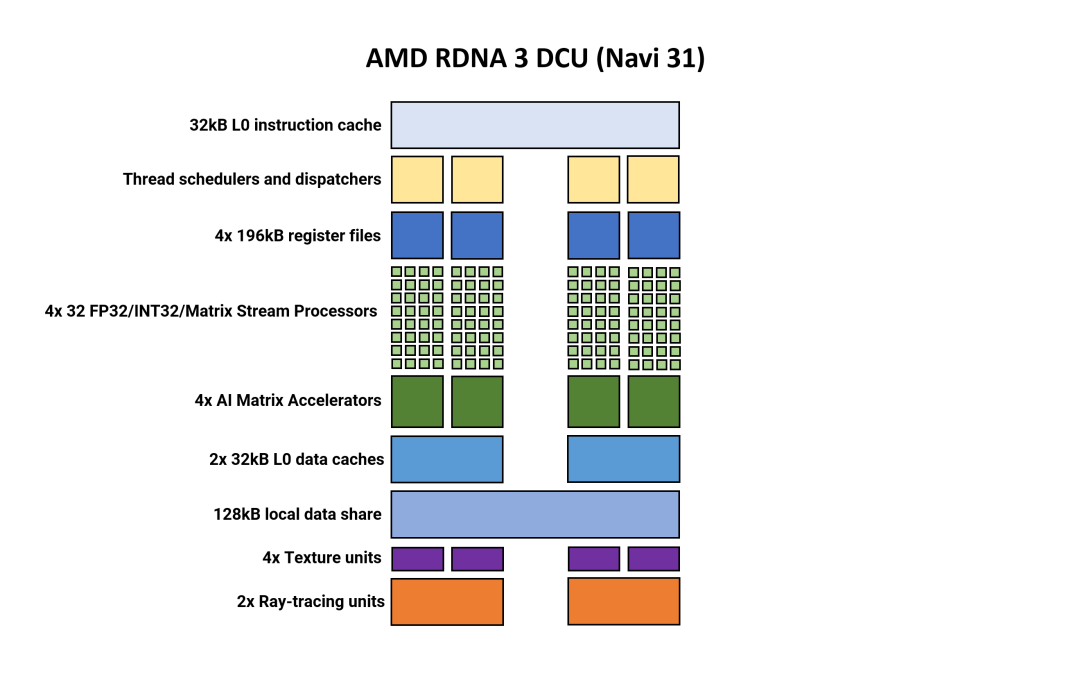

一、AMD RDNA 3

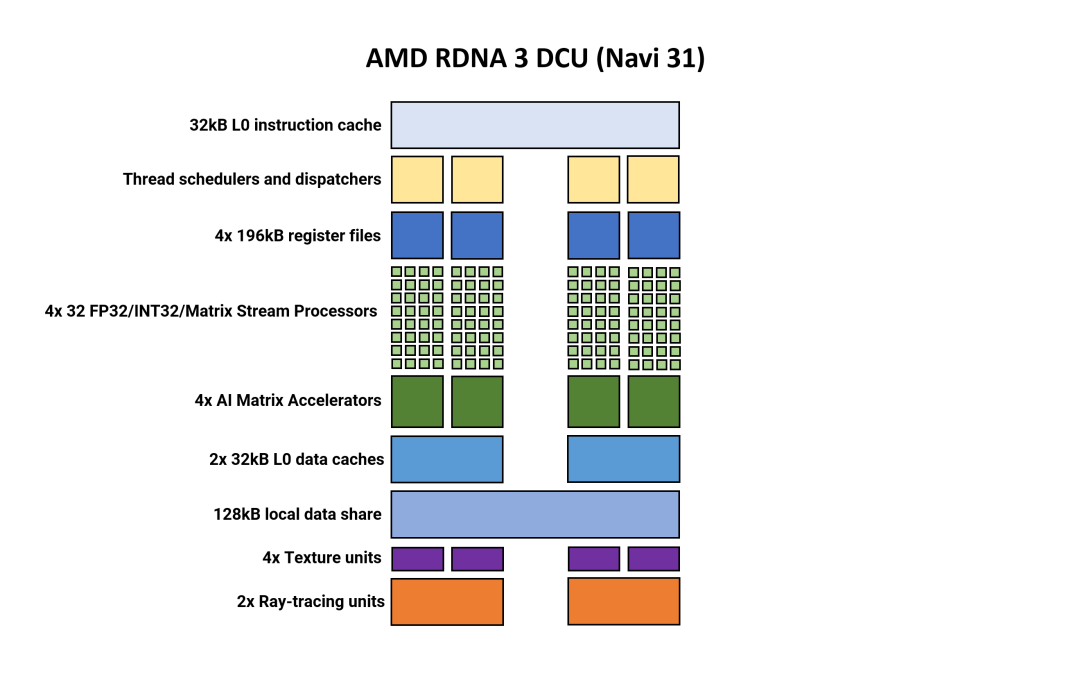

AMD GPU 着色部分内最小的统一结构称为双计算单元(DCU:Double Compute Unit)。在某些文档中,它仍然称为工作组处理器 (WGP:Workgroup Processor),而其他文档则将其称为计算单元对(CUP:Compute Unit Pair)。

请注意,如果这些图中未显示某些内容(例如常量缓存、双精度单元),并不意味着它们不存在于体系结构中。

在很多方面,整体布局和结构元素与 RDNA 2 相比并没有太大变化。两个计算单元共享一些缓存和内存,每个计算单元包含两组 32 个流处理器 (SP)。

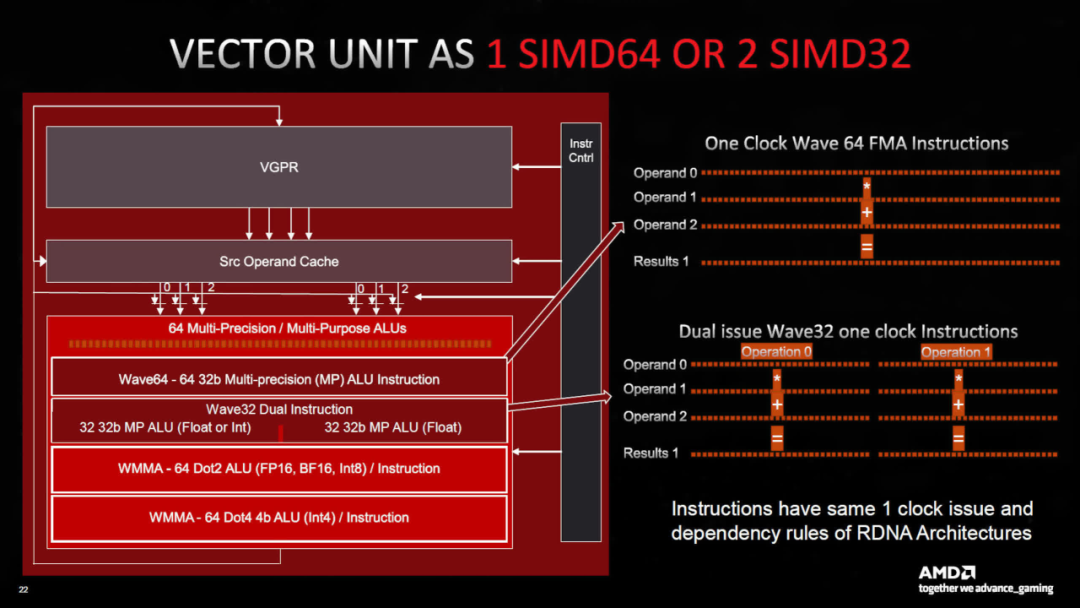

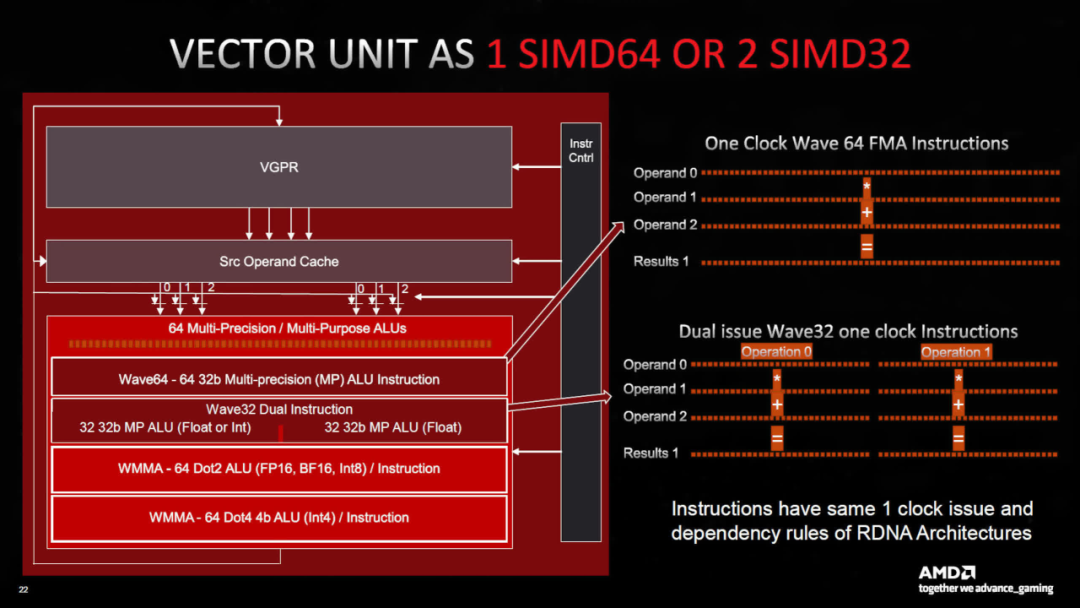

第 3 版的新增功能是,每个 SP 现在容纳的算术逻辑单元 (ALU:arithmetic logic units ) 数量是以前的两倍。现在,每个 CU 有两组 SIMD64 单元,每个组有两个数据端口——一个用于浮点、整数和矩阵运算,另一个仅用于浮点和矩阵运算。

AMD 确实针对不同的数据格式使用单独的 SP, RDNA 3 中的计算单元支持使用 FP16、BF16、FP32、FP64、INT4、INT8、INT16 和 INT32 值进行操作。

使用 SIMD64 意味着每个线程调度程序可以在每个时钟周期发出一组 64 个线程(称为wavefront),或者可以共同发出两个 32 个线程的波前。AMD 保留了与以前的 RDNA 架构相同的指令规则,因此这是由 GPU/驱动程序处理的。

另一个重要的新功能是 AMD 所谓的 AI 矩阵加速器的出现。

与我们很快就会看到的 Intel 和 Nvidia 的架构不同,它们并不充当单独的单元——所有矩阵运算都利用 SIMD 单元,并且任何此类计算(称为波矩阵乘法累加,WMMA:Wave Matrix Multiply Accumulate)都将使用完整的 64 个 ALU 组。

在撰写本文时,人工智能加速器的确切性质尚不清楚,但它可能只是与处理指令和涉及的大量数据相关的电路,以确保最大吞吐量。它很可能与 Nvidia 的Hopper 架构中的张量内存加速器具有类似的功能。

与 RDNA 2 相比,变化相对较小——较旧的架构还可以处理 64 个线程波前(又名 Wave64),但这些是在两个周期内发布的,并且在每个计算单元中使用两个 SIMD32 块。现在,这一切都可以在一个周期内完成,并且仅使用一个 SIMD 块。

在之前的文档中,AMD 表示 Wave32 通常用于计算和顶点着色器(也可能用于光线着色器),而 Wave 64 主要用于像素着色器,驱动程序会相应地编译着色器。因此,转向单周期 Wave64 指令问题将为严重依赖像素着色器的游戏带来推动。

然而,所有这些额外的可用功率都需要正确利用才能充分利用。所有 GPU 架构都是如此,并且它们都需要大量线程负载,才能做到这一点(这也有助于隐藏与 DRAM 相关的固有延迟)。

因此,随着 ALU 数量增加一倍,AMD 推动了程序员尽可能使用指令级并行性的需求。这在图形领域并不是什么新鲜事,但 RDNA 相对于 AMD 旧的 GCN 架构的一个显著优势是,它不需要那么多的运行线程来达到充分利用。鉴于现代渲染在游戏中变得多么复杂,开发人员在编写着色器代码时需要做更多的工作。

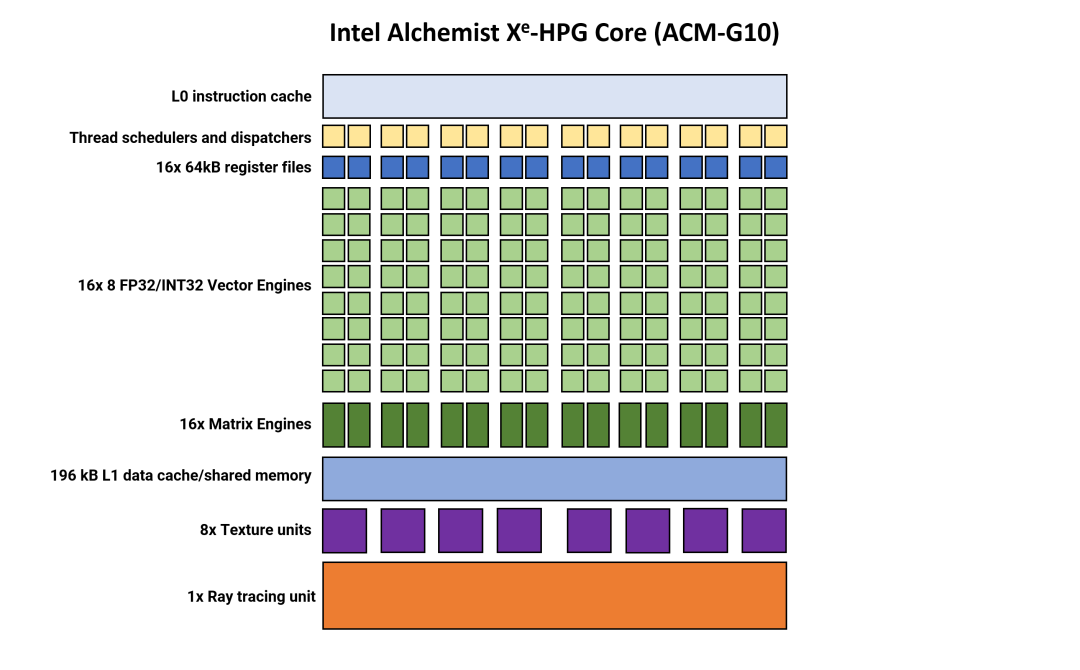

二、Intel Alchemist

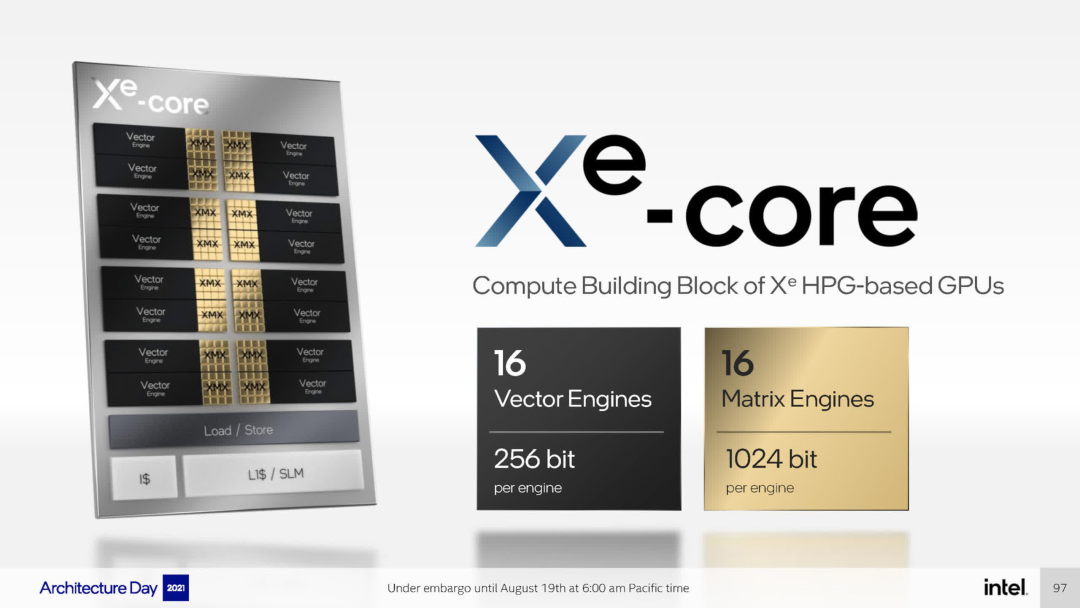

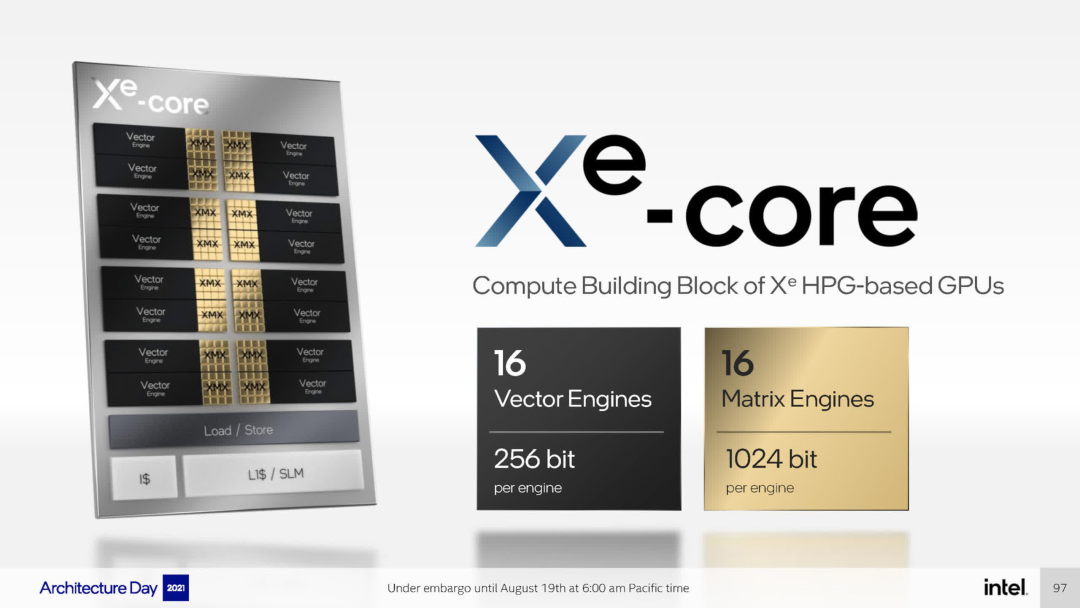

现在让我们转向英特尔,看看 Alchemist 架构中的 DCU 等效项,称为Xe Core(我们将其缩写为 XEC)。乍一看,与 AMD 的结构相比,这些看起来绝对是巨大的。

RDNA 3 中的单个 DCU 包含四个 SIMD64 块,而英特尔的 XEC 包含16 个SIMD8 单元,每个单元都由自己的线程调度程序和调度系统管理。与 AMD 的流处理器一样,Alchemist 中所谓的矢量引擎可以处理整数和浮点数据格式。不支持 FP64,但这在游戏中不是什么大问题。

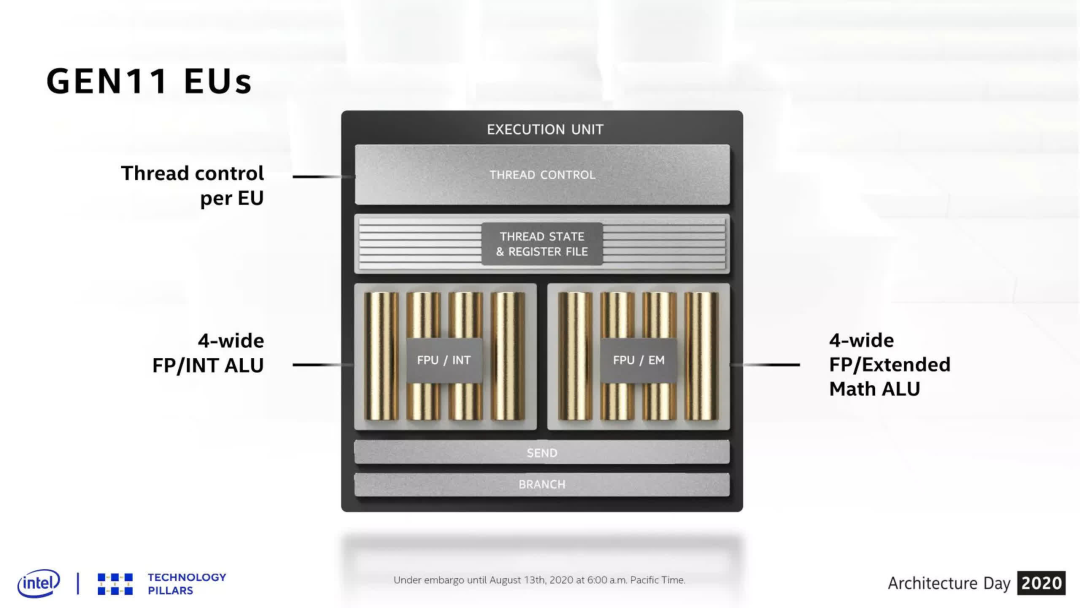

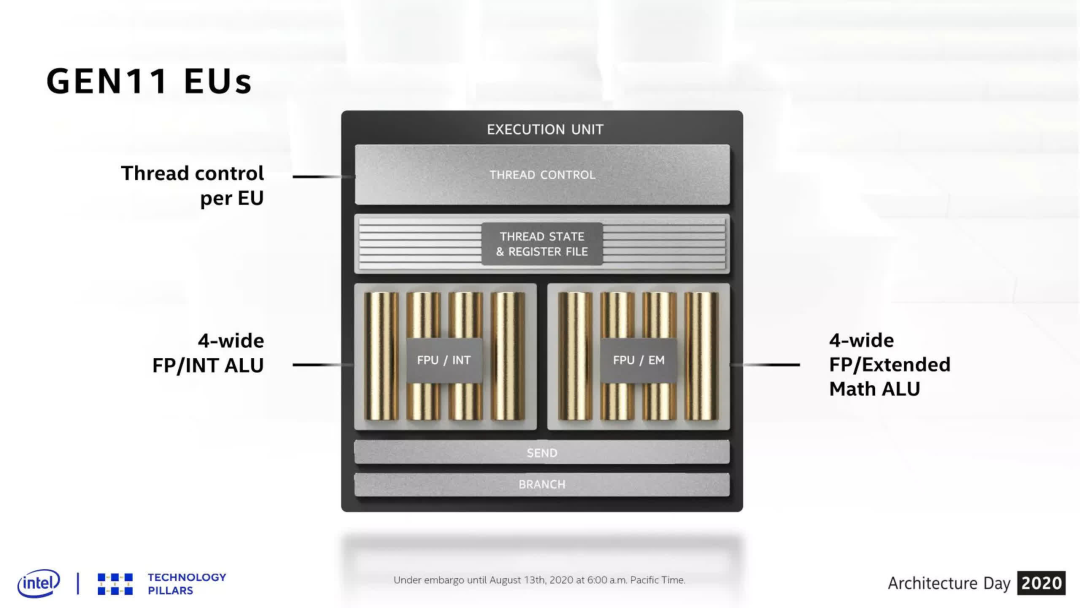

英特尔一直使用相对较窄的 SIMD——Gen11 中使用的 SIMD 仅为 4 宽(即同时处理 4 个线程),而 Gen 12 的宽度仅加倍(例如,在其 Rocket Lake CPU 中使用)。

但考虑到游戏行业已经使用 SIMD32 GPU 多年,因此游戏也进行了相应的编码,因此保留狭窄执行块的决定似乎会适得其反。

AMD 的 RDNA 3 和 Nvidia 的 Ada Lovelace 的处理块可以在一个周期内发出 64 或 32 个线程,而英特尔的架构需要 4 个周期才能在一个 VE 上实现相同的结果,因此每个 XEC 有 16 个 SIMD 单元。

然而,这意味着如果游戏的编码方式不能确保 VE 被完全占用,SIMD 和相关资源(缓存、带宽等)将处于闲置状态。英特尔Arc 系列显卡的基准测试结果的一个共同主题是,它们往往在更高的分辨率和/或具有大量复杂的现代着色器例程的游戏中表现更好。

这在一定程度上是由于单位细分和资源共享程度较高。Chips and Cheese网站的微基准分析表明,尽管拥有丰富的 ALU,该架构仍难以实现适当的利用。

转到 XEC 的其他方面,尚不清楚 0 级指令缓存有多大,但 AMD 的指令缓存是 4 路(因为它服务于四个 SIMD 块),而 Intel 的缓存必须是 16 路,这增加了复杂性缓存系统的。

英特尔还选择为处理器提供用于矩阵运算的专用单元,每个向量引擎对应一个单元。拥有如此多的单元意味着芯片的很大一部分专门用于处理矩阵数学。

AMD 使用 DCU 的 SIMD 单元来完成此操作,而 Nvidia 每个 SM 有四个相对较大的张量/矩阵单元,而英特尔的方法似乎有点过分,因为他们有一个单独的架构,称为 X e-HP,用于计算应用程序。

另一个奇怪的设计似乎是处理块中的加载/存储(LD/ST)单元。我们的图表中未显示,它们管理来自线程的内存指令,在寄存器文件和 L1 缓存之间移动数据。Ada Lovelace 与 Ampere 相同,每个 SM 分区有 4 个,总共 16 个。RDNA 3 也与其前身相同,每个 CU 都有专用的 LD/ST 电路作为纹理单元的一部分。

英特尔的 Xe-HPG 演示显示每个 XEC 仅一个 LD/ST,但实际上,它内部可能由更多分立单元组成。然而,在他们的OneAPI优化指南中,一张图表表明 LD/ST 一次循环一个单独的寄存器文件。如果是这种情况,那么 Alchemist 将始终难以实现最大缓存带宽效率,因为并非所有文件都同时得到服务。

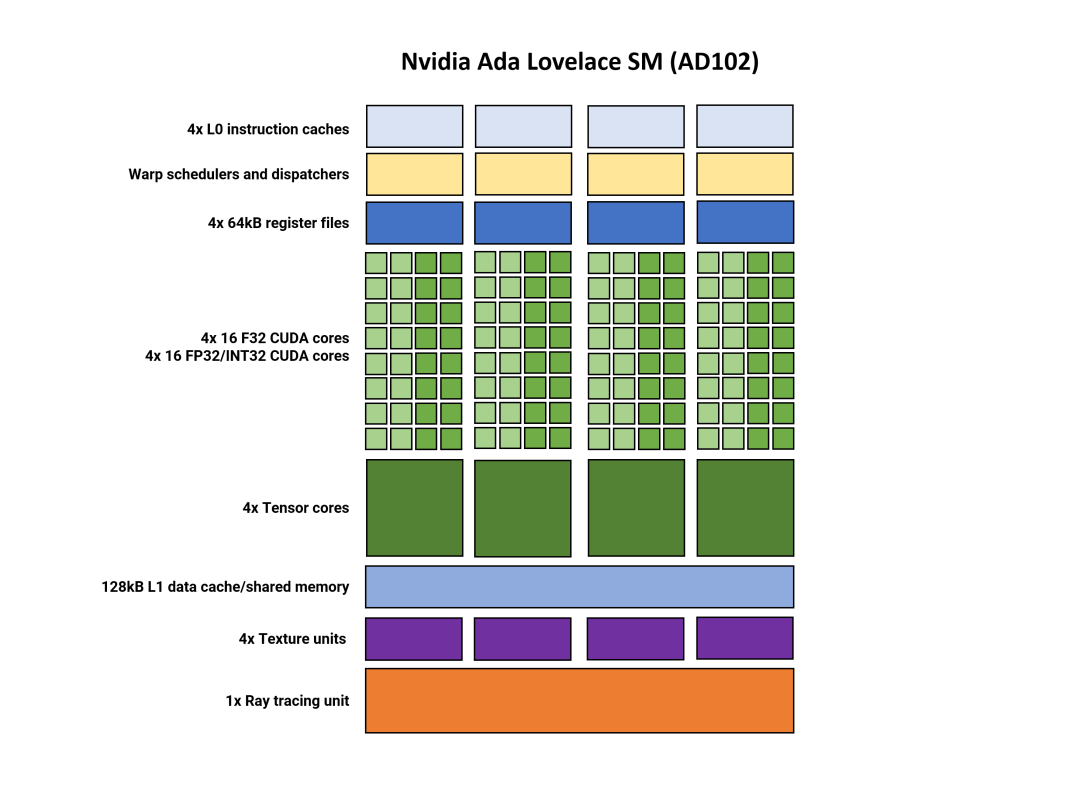

三、Nvidia Ada Lovelace

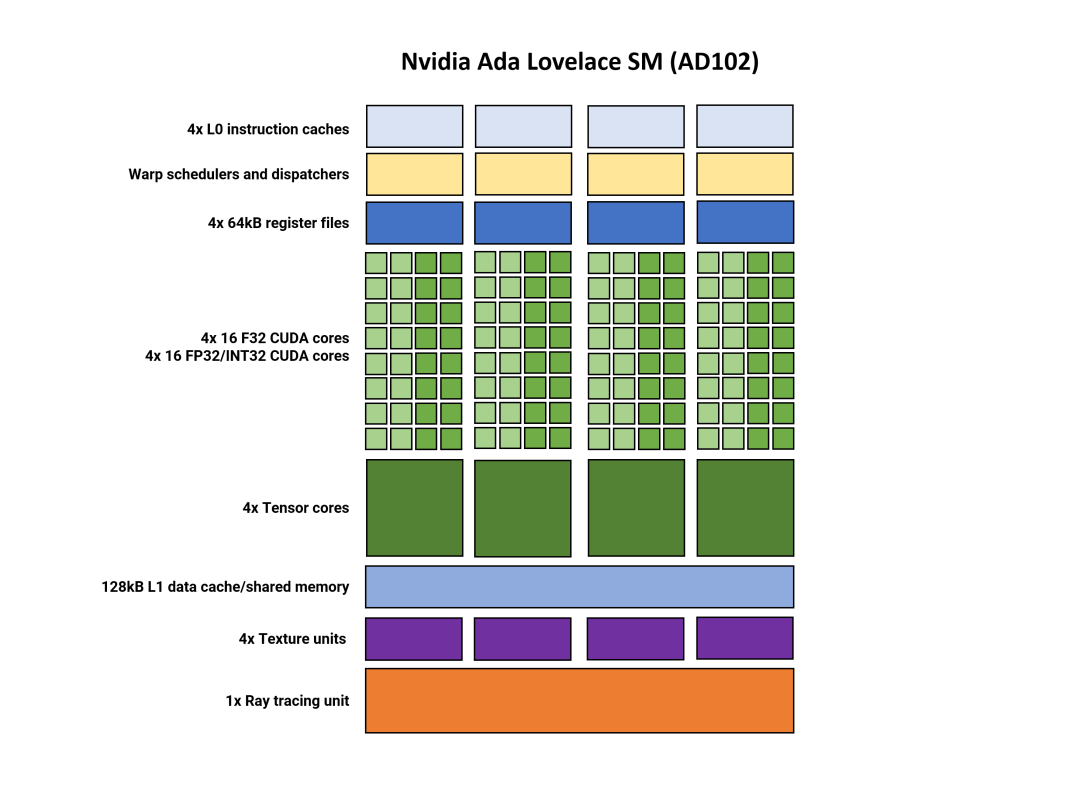

最后一个需要关注的处理模块是 Nvidia 的流式多处理器(SM:Streaming Multiprocessor ) – DCU/XEC 的 GeForce 版本。这个结构与2018年的图灵架构相比并没有太大的改变。事实上,它几乎与Ampere相同。

一些单元已经过调整以提高其性能或功能集,但在大多数情况下,没有太多新的东西可以谈论。事实上,可能有,但众所周知,英伟达不愿透露太多有关其芯片的内部操作和规格的信息。英特尔提供了更多细节,但这些信息通常隐藏在其他文档中。

但总结一下结构,SM 分为四个分区。每个处理器都有自己的 L0 指令缓存、线程调度程序和分派单元,以及与 SIMD32 处理器配对的 64 kB 寄存器文件部分。

正如AMD的RDNA 3一样,SM支持双发出指令,其中每个分区可以同时处理两个线程,一个使用FP32指令,另一个使用FP32或INT32指令。

Nvidia 的 Tensor 核心现已进入第四版,但这一次,唯一显著的变化是包含了Hopper 芯片中的FP8 Transformer 引擎,原始吞吐量数据保持不变。

低精度浮点格式的加入意味着GPU应该更适合AI训练模型。Tensor 核心还提供Ampere 的稀疏功能,可提供高达两倍的吞吐量。

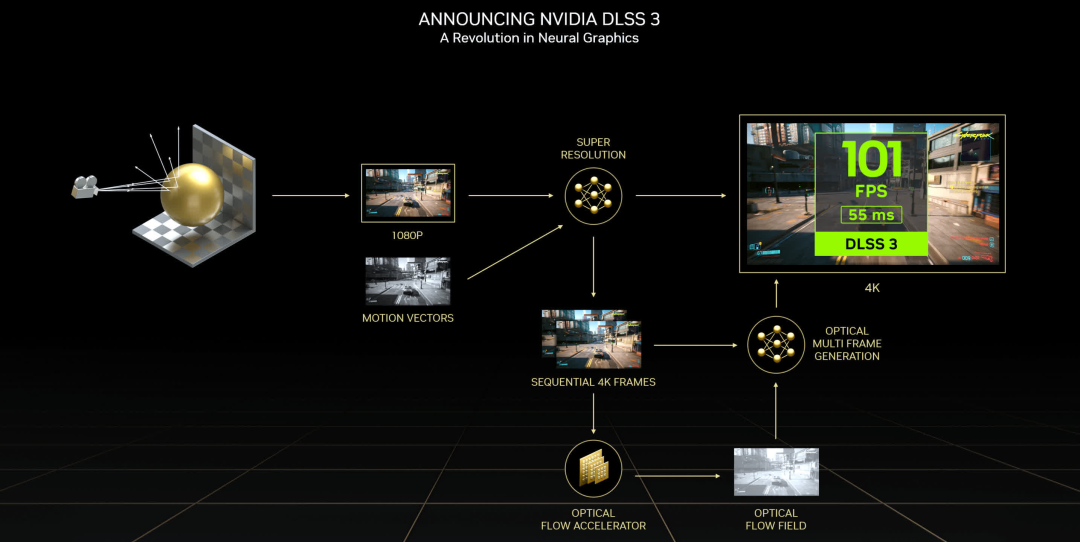

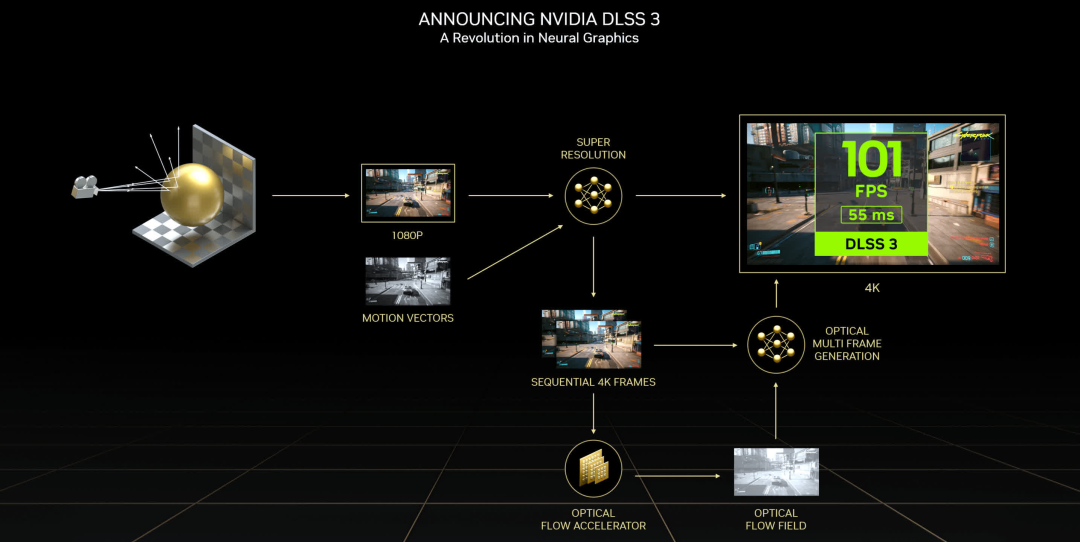

另一个改进在于光流加速器 (OFA:Optical Flow Accelerator) 引擎(图中未显示)。该电路生成光流场( optical flow field),用作DLSS算法的一部分。OFA 的安培性能提高了一倍,额外的吞吐量被用在最新版本的临时抗锯齿升频器 DLSS 3 中。

DLSS 3已经面临相当多的批评,主要集中在两个方面:DLSS 生成的帧不是“真实的”,并且该过程给渲染链增加了额外的延迟。第一个并不是完全无效,因为系统的工作原理是首先让 GPU 渲染两个连续的帧,将它们存储在内存中,然后使用神经网络算法确定中间帧的样子。

然后,当前链返回到第一个渲染帧并显示该帧,然后是 DLSS 帧,然后是渲染的第二帧。由于游戏引擎尚未在中帧循环,因此屏幕会在没有任何潜在输入的情况下刷新。而且由于需要停止而不是呈现两个连续的帧,因此为这些帧轮询的任何输入也将停止。

DLSS 3 是否会变得流行或普遍还有待观察。

尽管 Ada 的 SM 与 Ampere 非常相似,但 RT 内核有显着的变化,我们将很快解决这些变化。现在我们来总结一下AMD、Intel、Nvidia的GPU重复结构的计算能力。

处理块比较

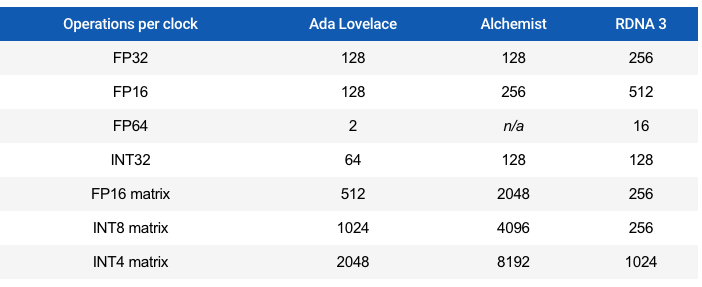

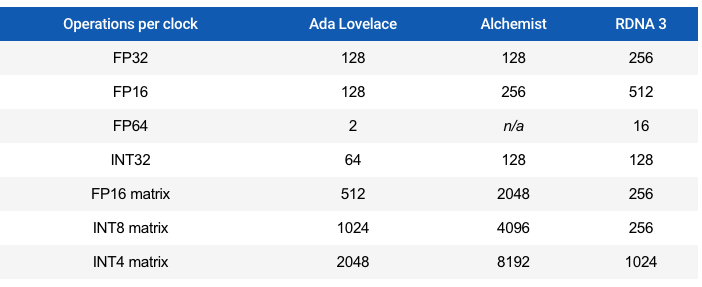

我们可以通过查看每个时钟周期的标准数据格式的操作数量来比较 SM、XEC 和 DCU 的功能。请注意,这些是峰值数字,实际上不一定可以实现。

Nvidia 的数字与 Ampere 相比没有变化,而 RDNA 3 的数字在某些领域增加了一倍。然而,Alchemist在矩阵运算方面处于另一个水平,尽管应该再次强调这些是峰值理论值的事实。

鉴于英特尔的图形部门像英伟达一样严重依赖数据中心和计算,因此看到该架构将如此多的芯片空间用于矩阵运算也就不足为奇了。缺乏 FP64 功能并不是问题,因为该数据格式并未真正用于游戏,并且该功能存在于其 X e -HP 架构中。

理论上,在矩阵/张量运算方面,Ada Lovelace 和 Alchemist 比 RDNA 3 更强,但由于我们正在研究主要用于游戏工作负载的 GPU,因此专用单元大多只是为 DLSS 和相关算法提供加速。XeSS——它们使用卷积自动编码器神经网络(CAENN)来扫描图像中的伪影并进行纠正。

AMD 的时间升级器(FidelityFX Super Resolution, FSR))不使用 CAENN,因为它主要基于Lanczos 重采样方法,然后是通过 DCU 处理的许多图像校正例程。然而,在RDNA 3 的发布中,简要介绍了FSR 的下一版本,并引用了一项名为“Fluid Motion Frames”的新功能。FSR 2.0 的性能提升高达两倍,普遍的共识是这可能涉及帧生成,如 DLSS 3 中那样,但这是否涉及任何矩阵运算尚不清楚。

适合每个人的光线追踪

随着使用 Alchemist 架构的 Arc 显卡系列的推出,英特尔与 AMD 和 Nvidia 一起提供 GPU,为图形中使用光线追踪所涉及的各种算法提供专用加速器。Ada 和 RNDA 3 都包含显着更新的 RT 单元,因此了解一下新的和不同的内容是有意义的。

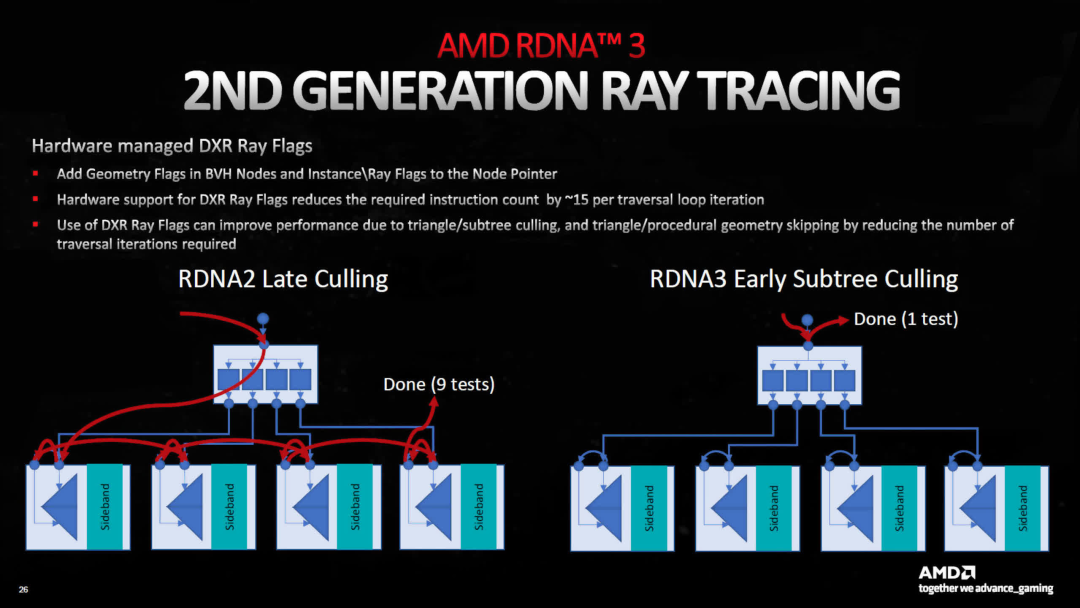

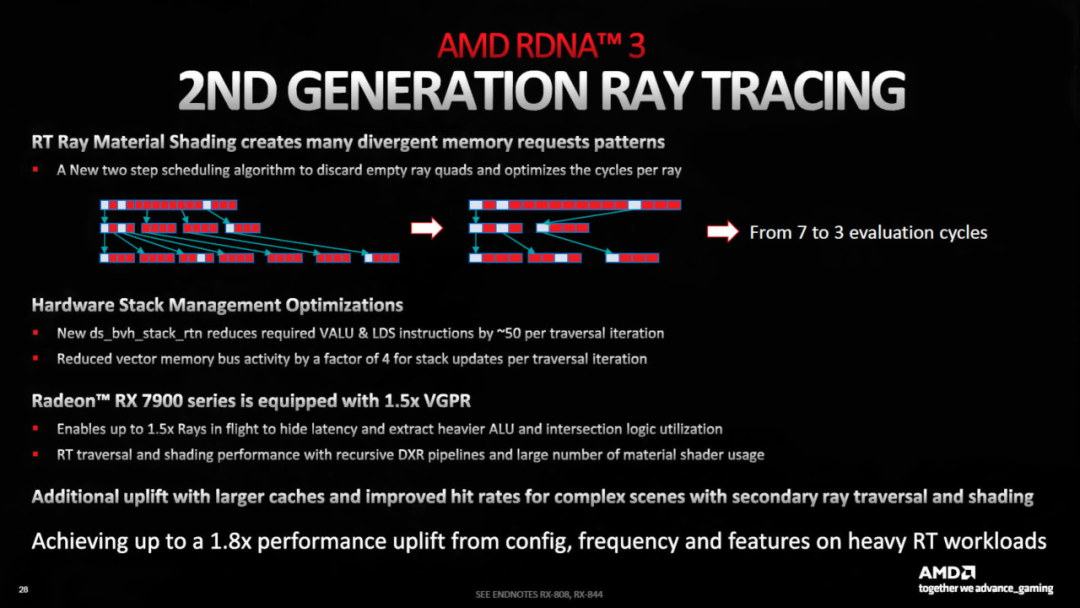

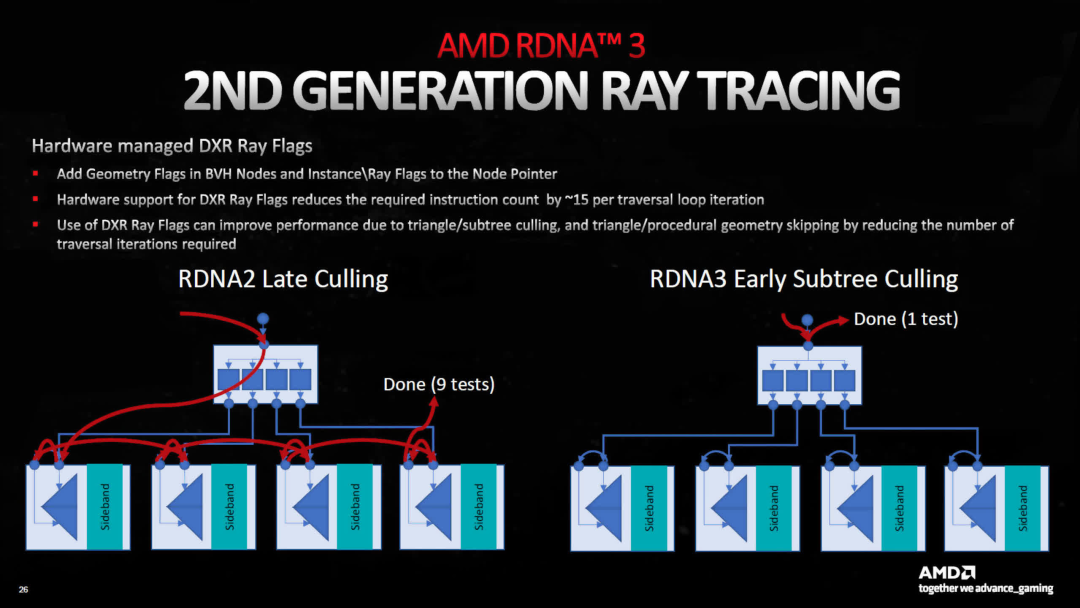

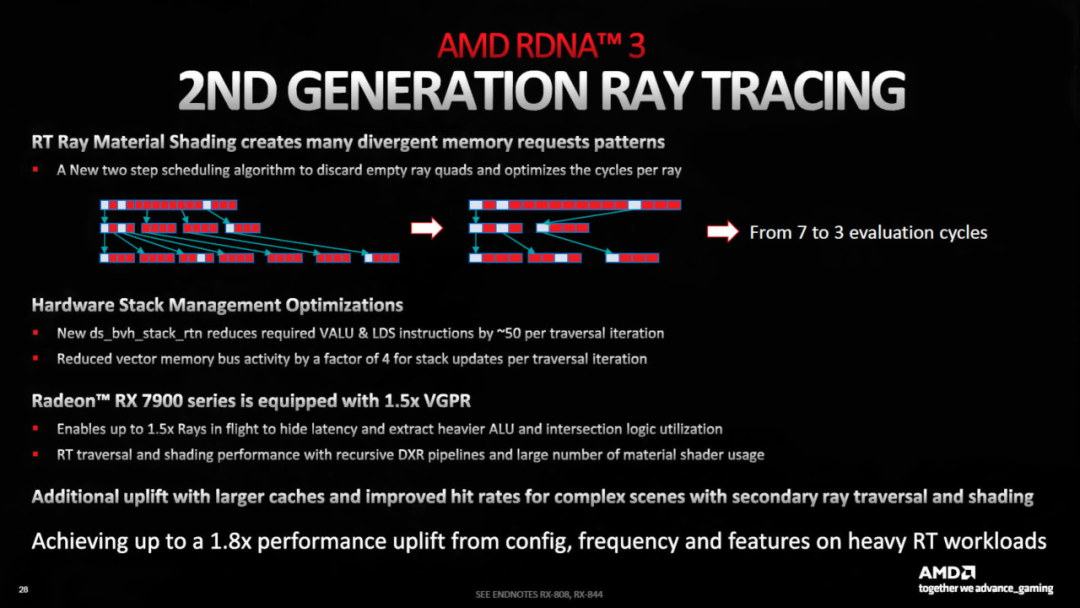

从 AMD 开始,其光纤加速器的最大变化是添加硬件以改进包围体层次结构(BVH:bounding volume hierarchies)的遍历(traversal)。这些数据结构用于加速确定 3D 世界中光线照射到的表面。

在 RDNA 2 中,所有这些工作都是通过计算单元处理的,并且在某种程度上仍然如此。然而,对于 DXR(微软的光线追踪 API)来说,有对光线标志管理的硬件支持。

使用这些可以大大减少需要遍历 BVH 的次数,从而减少缓存带宽和计算单元的总体负载。本质上,AMD 专注于提高他们在之前架构中引入的系统的整体效率。

此外,硬件已更新,以改进盒子排序(box sorting,这使得遍历更快)和剔除算法(culling algorithms,以跳过测试空盒子)。再加上缓存系统的改进,AMD 表示,在相同的时钟速度下,与 RDNA 2 相比,光线追踪性能提高了 80%。

然而,这种改进并不能转化为使用光线追踪的游戏中每秒帧数增加 80% ,这些情况下的性能受到许多因素的影响,RT 单元的功能只是其中之一。

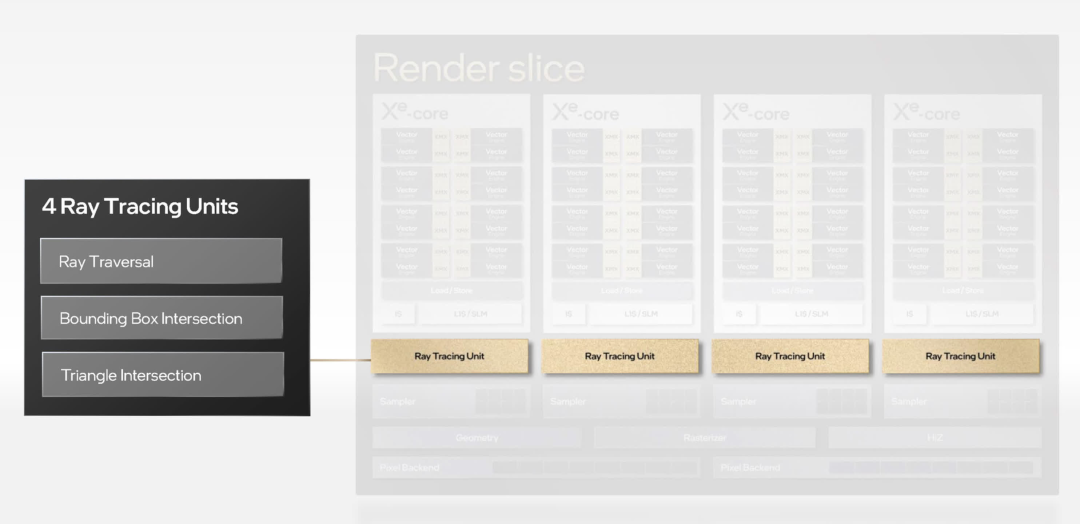

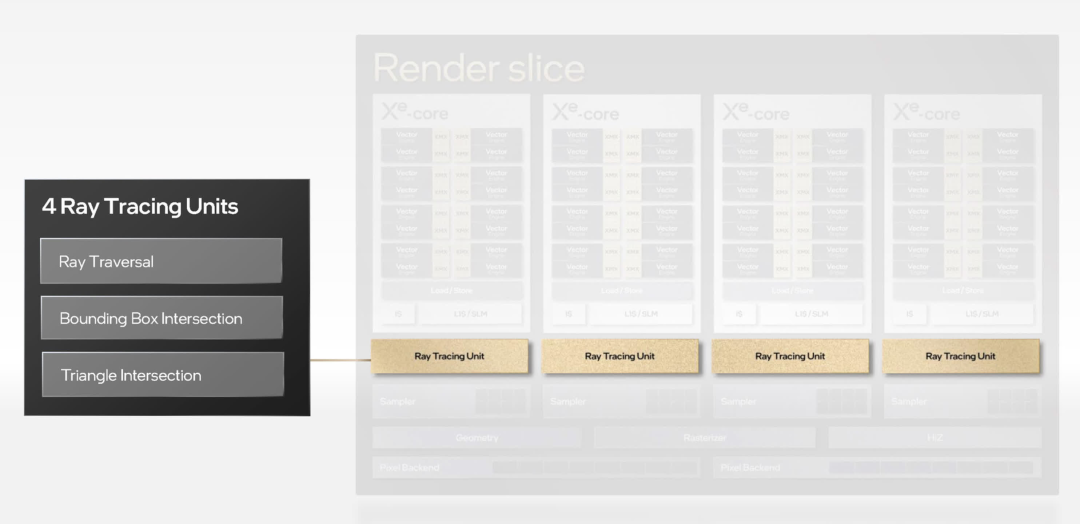

由于英特尔是光线追踪技术的新手,因此没有任何改进。相反,我们只是被告知他们的 RT 单元处理射线和三角形之间的 BVH 遍历和相交计算。这使得它们比 AMD 的系统更类似于 Nvidia 的系统,但关于它们的信息并不多。

但我们确实知道每个 RT 单元都有一个未指定大小的缓存用于存储 BVH 数据,以及一个单独的单元用于分析和排序光线着色器线程,以提高 SIMD 利用率。

每个 XEC 与一个 RT 单元配对,每个渲染切片总共有四个。在游戏中启用光线追踪的A770 的一些早期测试表明,无论英特尔采用何种结构,Alchemist 的光线追踪整体能力至少与 Ampere 芯片一样好,并且比 RDNA 2 型号稍好一些。

但让我们再次重申,光线追踪也给着色核心、缓存系统和内存带宽带来了沉重压力,因此不可能从此类基准测试中提取 RT 单元性能。

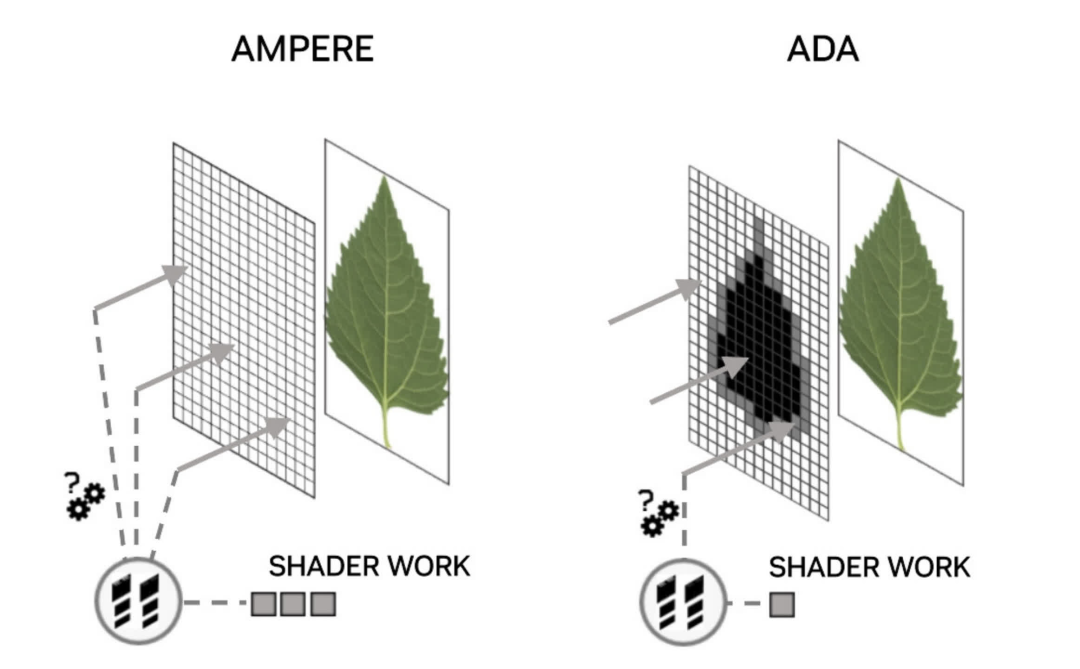

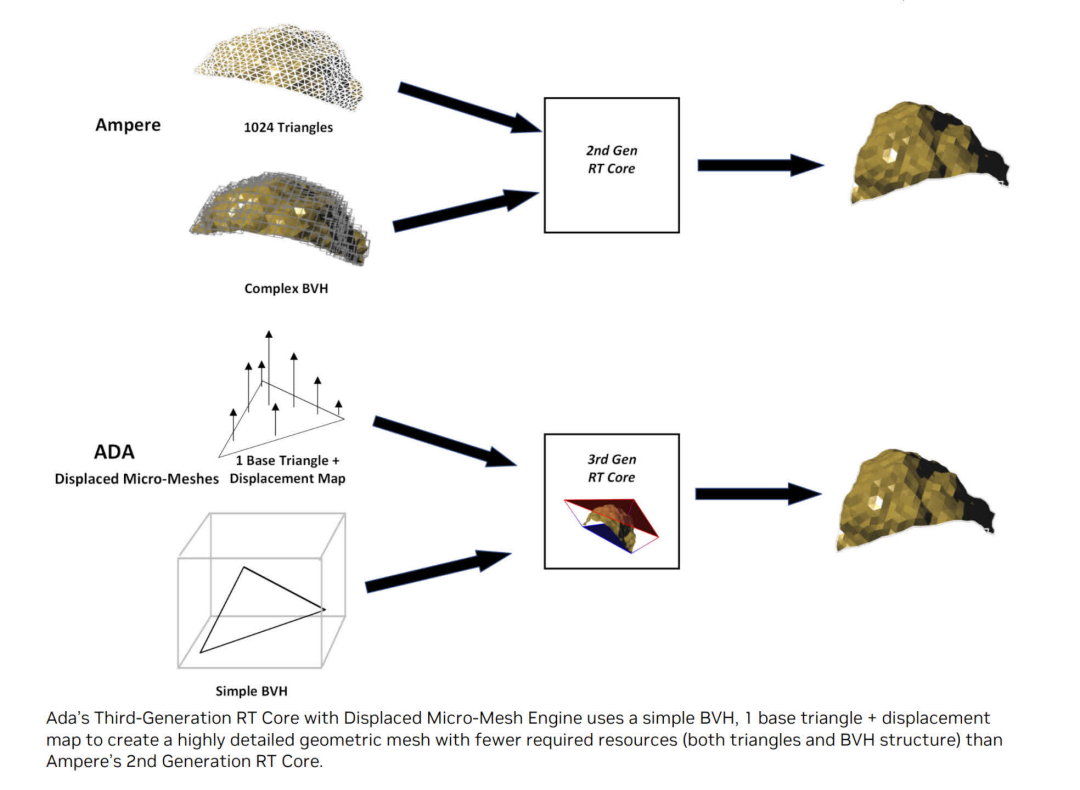

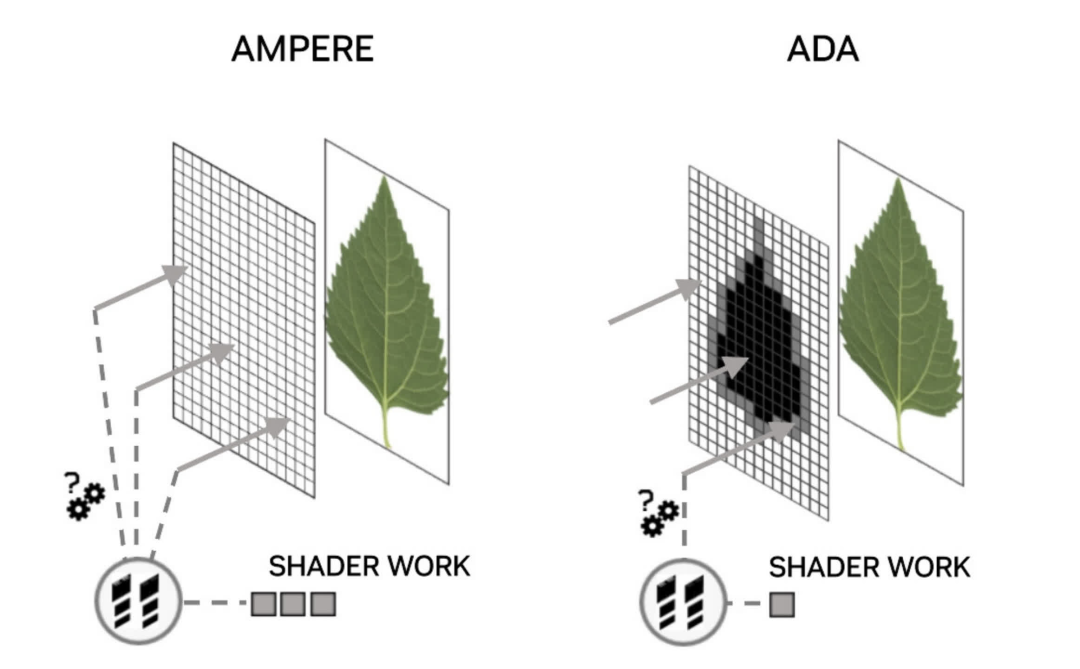

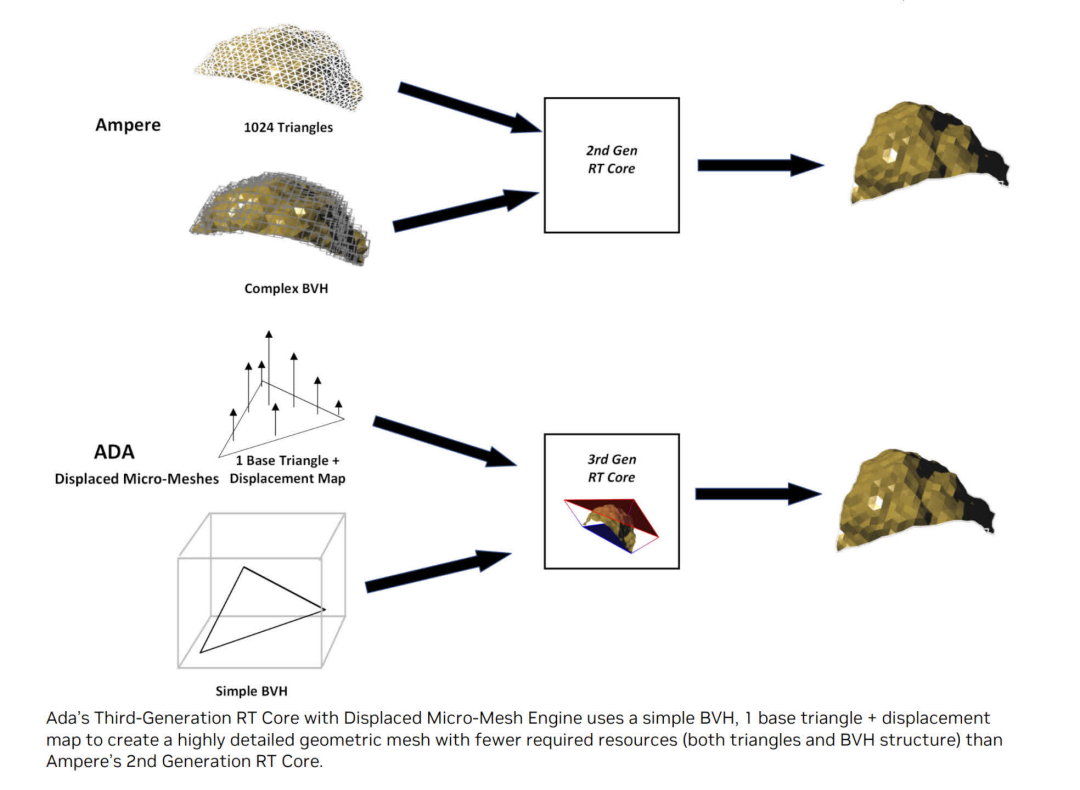

对于 Ada Lovelace 架构,Nvidia 做出了许多改变,与 Ampere 相比,其性能提升幅度相当大。据称,用于射线-三角形相交计算的加速器的吞吐量提高了一倍,并且现在据说非不透明表面的 BVH 遍历速度提高了一倍。后者对于使用带有 alpha channel (透明度)的纹理的对象很重要,例如树上的叶子。

光线击中此类表面的完全透明部分不应导致击中结果——光线应直接穿过。然而,为了在当前使用光线追踪的游戏中准确确定这一点,需要处理多个其他着色器。Nvidia 的新不透明度微贴图引擎将这些表面分解成更多的三角形,然后确定到底发生了什么,从而减少了所需的光线着色器的数量。

Ada 光线追踪功能的另外两个附加功能是减少 BVH 的构建时间和内存占用(声称速度分别加快 10 倍和缩小 20 倍),以及为光线着色器重新排序线程的结构,从而提高效率。然而,前者不需要开发人员对软件进行任何更改,而后者目前只能通过 Nvidia 的 API 访问,因此对当前的 DirectX 12 游戏没有任何好处。

当我们测试 GeForce RTX 4090 的光线追踪性能时,启用光线追踪后帧速率的平均下降略低于 45%。使用 Ampere 驱动的 GeForce RTX 3090 Ti 时,下降了 56%。然而,这种改进不能完全归因于 RT 核心的改进,因为 4090 比以前的型号具有更多的着色吞吐量和缓存。

我们还没有看到 RDNA 3 的光线追踪改进会产生什么样的差异,但值得注意的是,没有一家 GPU 制造商期望单独使用 RT – 即仍然需要使用升级来实现高帧速率。

光线追踪的粉丝可能会有些失望,因为新一轮的图形处理器在这一领域没有取得任何重大进展,但自 2018 年 Nvidia 图灵架构首次出现以来,已经取得了很多进展。

内存:沿着数据高速公路行驶

GPU 处理数据的方式与其他芯片不同,而让 ALU 保持数据输入对其性能至关重要。在 PC 图形处理器的早期,内部几乎没有任何缓存,全局内存(整个芯片使用的 RAM)是非常慢的 DRAM。即使就在10年前,情况也没有好多少。

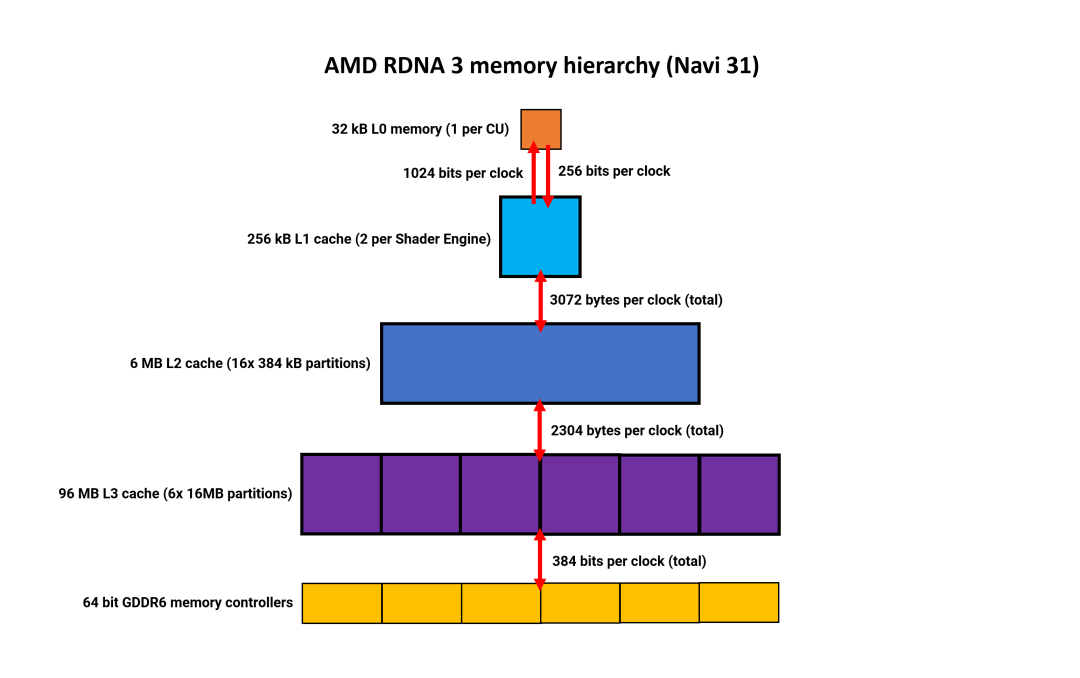

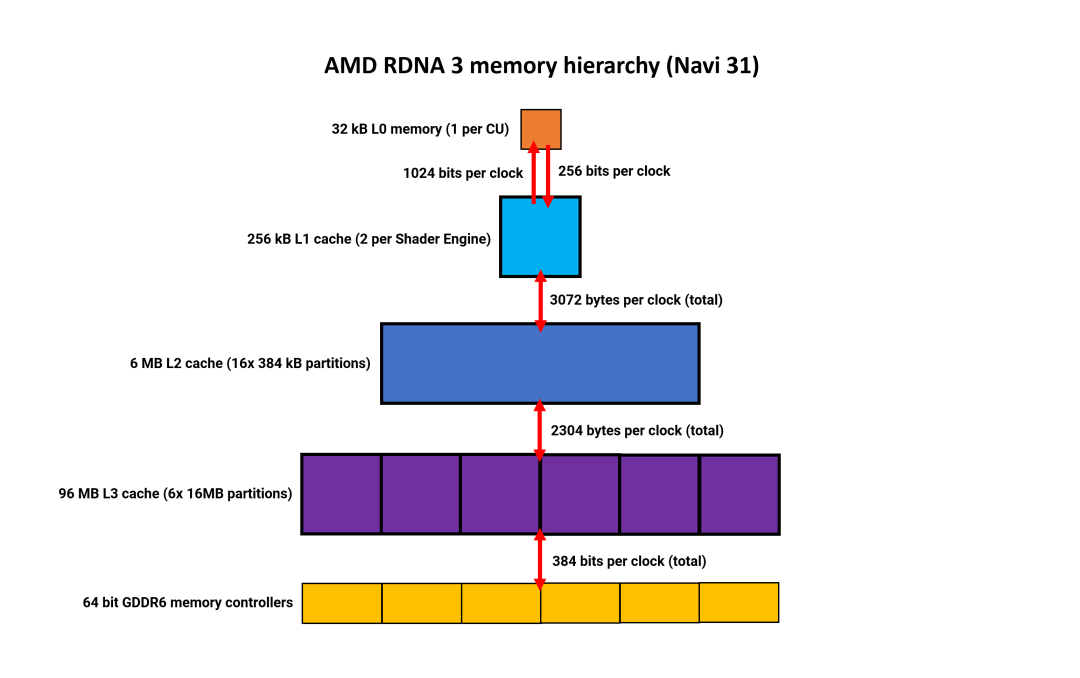

因此,让我们从 AMD 新架构中的内存层次结构开始,深入了解当前的情况。自第一次迭代以来,RDNA 使用了复杂的多级内存层次结构。最大的变化发生在一年前,当时 GPU 中添加了大量的 L3 缓存,在某些型号中高达 128MB。

第三轮的情况仍然如此,但有一些微妙的变化。

Nvidia 保留了与 Ampere 中使用的相同的内存结构,每个 SM 具有 128kB 的缓存,充当 L1 数据存储、共享内存和纹理缓存。可用于不同角色的数量是动态分配的。目前尚未提及 L1 带宽的任何变化,但在 Ampere 中,每个 SM 每个时钟周期为 128 字节。Nvidia 从未明确明确这一数字是累积的、结合读写的,还是仅针对一个方向的。

如果 Ada 至少与 Ampere 相同,那么所有 SM 的总 L1 带宽将达到每个时钟 18 kB,远大于 RDNA 2 和 Alchemist。

但必须再次强调的是,这些芯片不具有直接可比性,因为英特尔的芯片是作为中端产品定价和销售的,而 AMD 已明确表示Navi 31 的设计目的从来不是为了与 Nvidia 的 AD102 竞争。它的竞争对手是 AD103,它比 AD102 小得多。

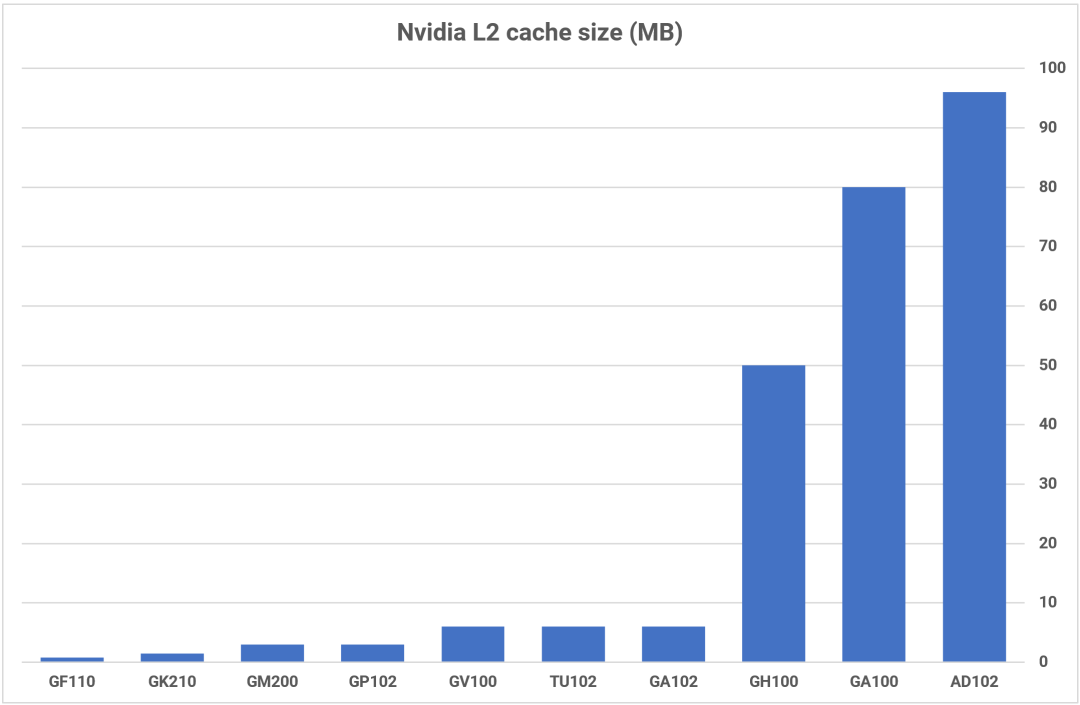

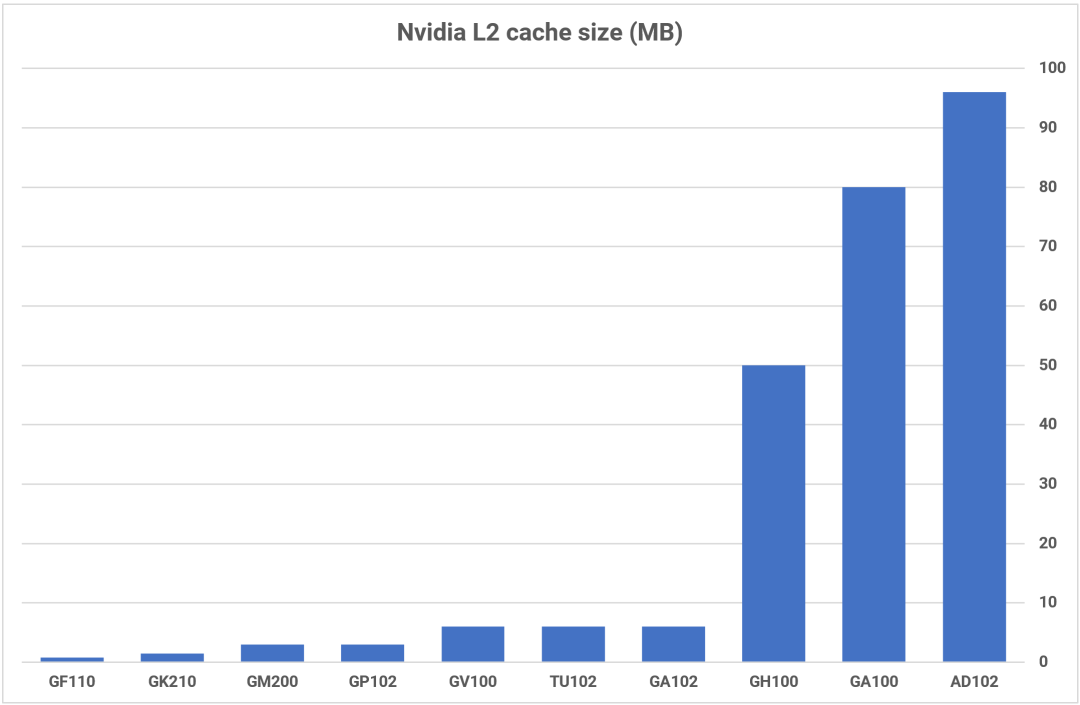

内存层次结构的最大变化是,在完整的 AD102 芯片中,L2 缓存已增加到 96MB,是其前身 GA102 的 16 倍。与英特尔的系统一样,L2 进行分区并与 32 位 GDDR6X 内存控制器配对,以实现高达 384 位的 DRAM 总线宽度。

较大的缓存通常比较小的缓存具有更长的延迟,但由于时钟速度的提高和总线的一些改进,Ada Lovelace 显示出比 Ampere更好的缓存性能。

如果我们比较所有三个系统,英特尔和 Nvidia 对 L1 缓存采取相同的方法 -——它可以用作只读数据缓存或计算共享内存。对于后者,需要通过软件明确指示 GPU 以这种格式使用它,并且数据仅在使用它的线程处于活动状态时保留。这增加了系统的复杂性,但对计算性能产生了有用的提升。

在 RDNA 3 中,“L1”数据缓存和共享内存被分为两个 32kB L0 矢量缓存和一个 128kB 本地数据共享。AMD 所谓的 L1 缓存实际上是一组四个 DCU 和 L2 缓存之间用于只读数据的共享垫脚石(shared stepping stone)。

虽然缓存带宽没有 Nvidia 的那么高,但多层方法有助于解决这个问题,尤其是在 DCU 未得到充分利用的情况下。

巨大的处理器范围的缓存系统通常不是 GPU 的最佳选择,这就是为什么我们在以前的架构中没有看到超过 4 或 6MB 的缓存系统,但 AMD、Intel 和 Nvidia 都在最后一层是应对 DRAM 速度增长相对不足的问题。

向 GPU 添加大量内存控制器可以提供充足的带宽,但代价是芯片尺寸增加和制造费用增加,而 HBM3 等替代方案的使用成本要高得多。

我们还没有看到 AMD 的系统最终表现如何,但他们在 RDNA 2 中的四层方法在与 Ampere 的对抗中表现良好,并且比英特尔的系统要好得多。然而,随着 Ada 加入了更多的 L2,竞争不再那么简单。

芯片封装和工艺节点:建造的不同方式

AMD、英特尔和 Nvidia 有一个共同点——他们都使用台积电来制造 GPU。

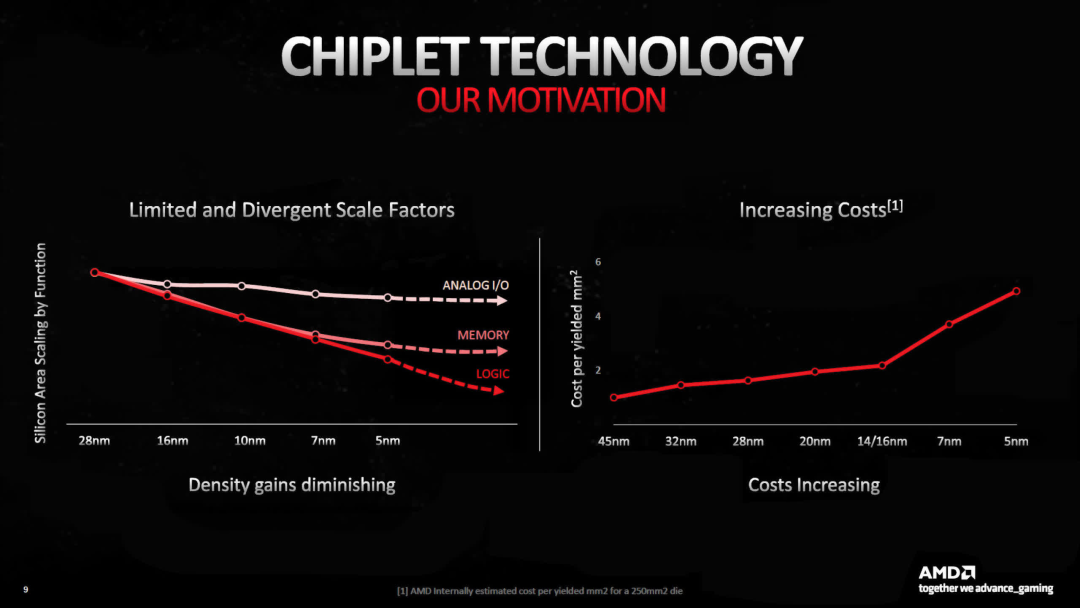

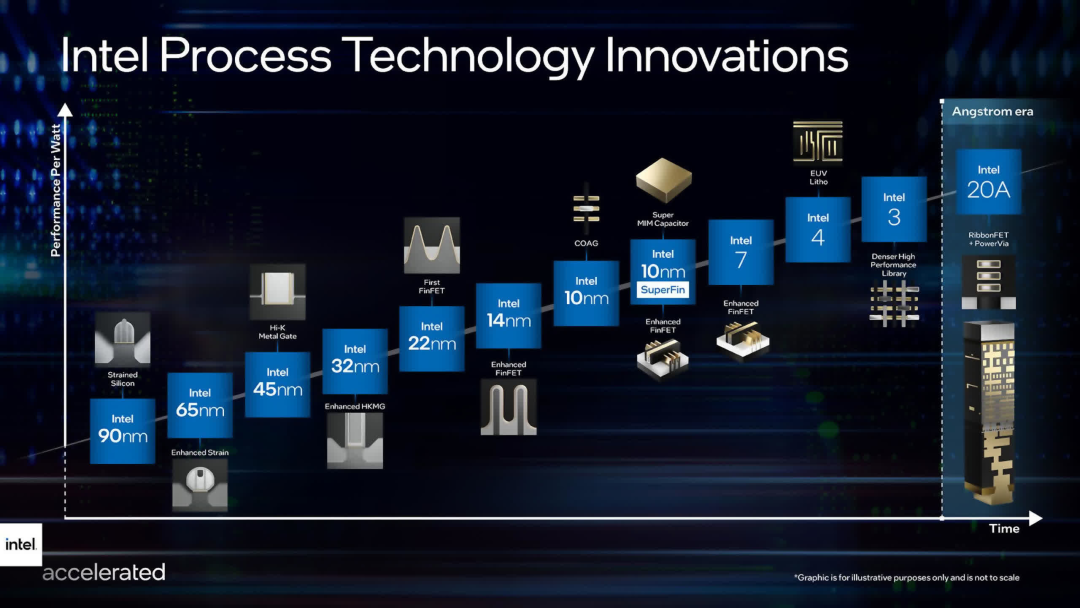

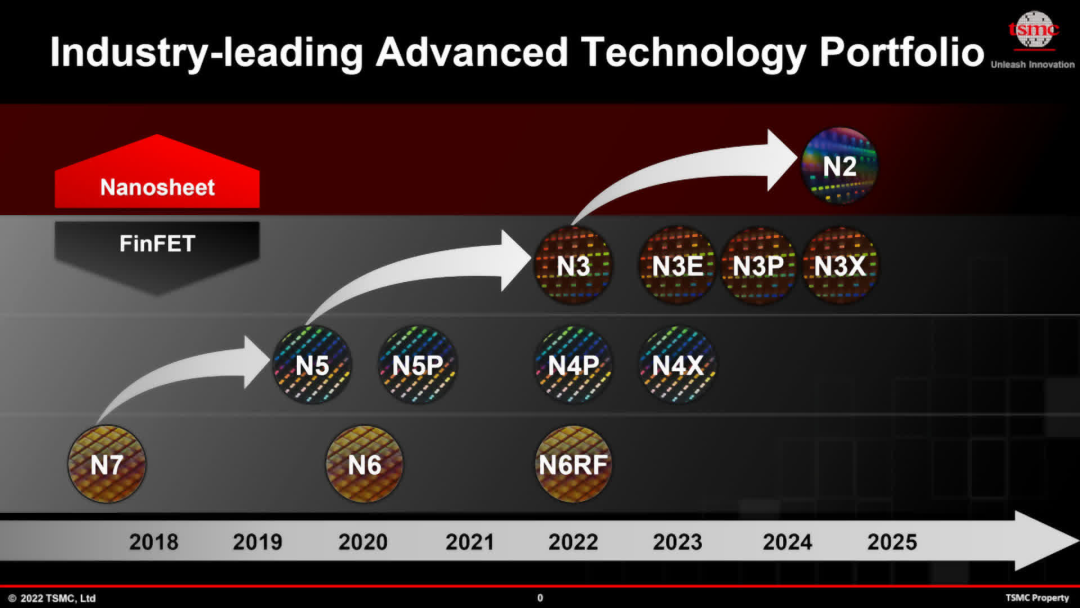

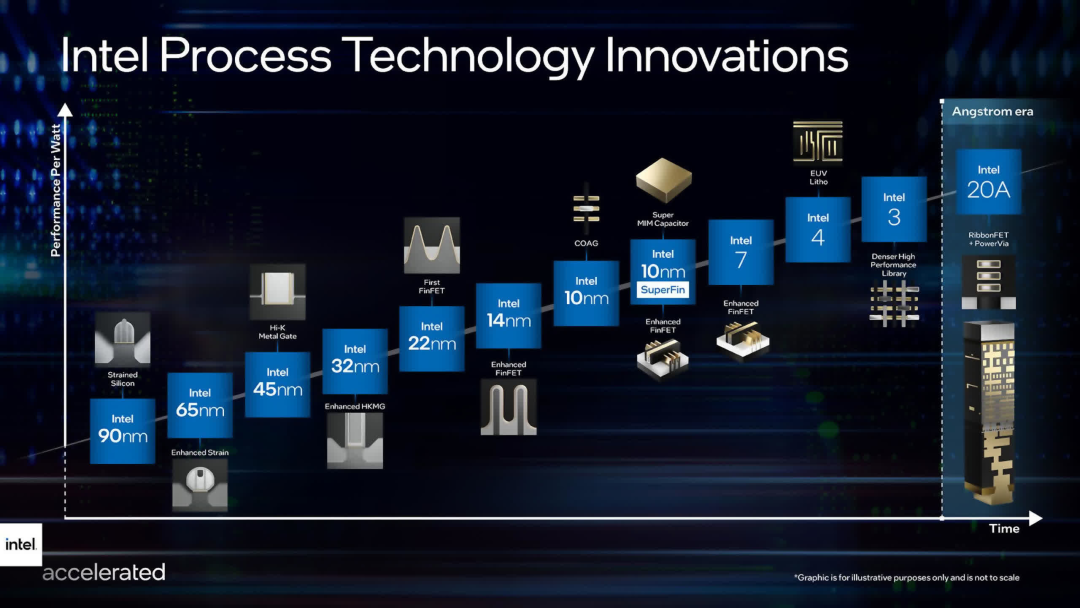

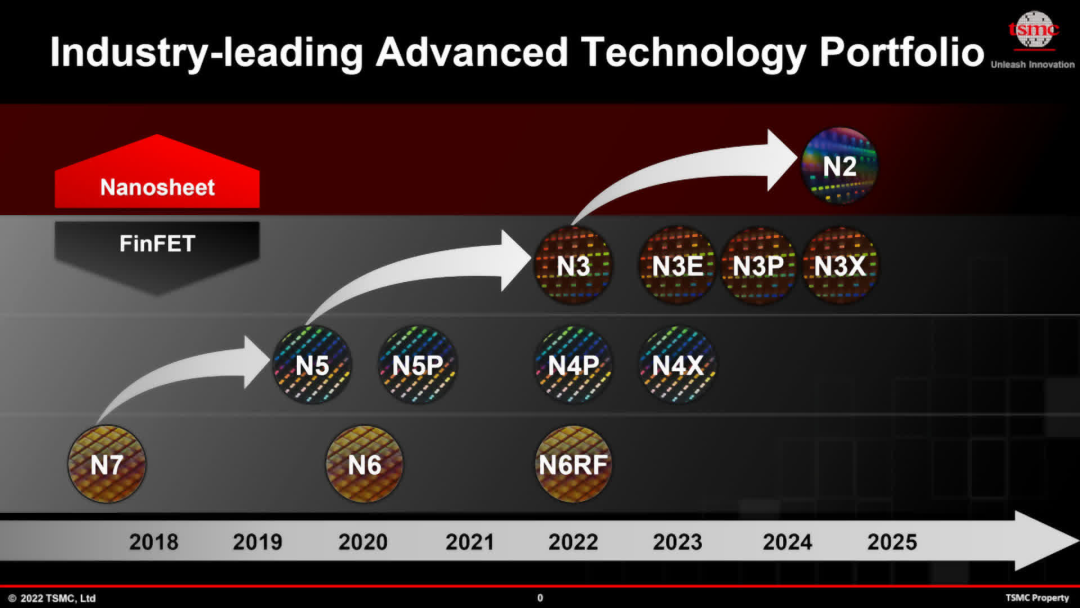

AMD在Navi 31中的GCD和MCD使用了两种不同的节点,前者使用N5节点,后者使用N6(N7的增强版本)。英特尔还在其所有 Alchemist 芯片中使用 N6。在 Ampere 中,Nvidia 使用了三星旧的 8nm 工艺,但在 Ada 中,他们转回台积电及其 N4 工艺,这是 N5 的变体。

N4 拥有所有节点中最高的晶体管密度和最佳的性能功耗比,但当 AMD 推出 RDNA 3 时,他们强调只有逻辑电路的密度出现了显着增加。

SRAM(用于高速缓存)和模拟系统(用于存储器、系统和其他信号电路)微缩相对较小。再加上新工艺节点每晶圆价格的上涨,AMD 决定使用稍旧且更便宜的 N6 来制造 MCD,因为这些小芯片主要是 SRAM 和 I/O。

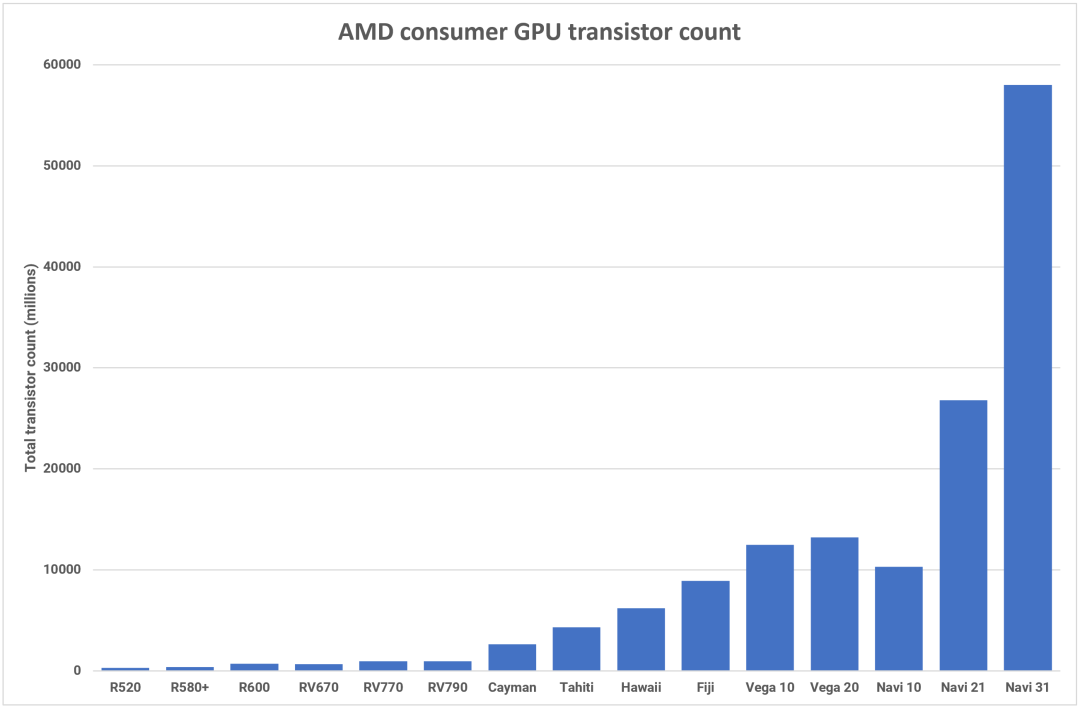

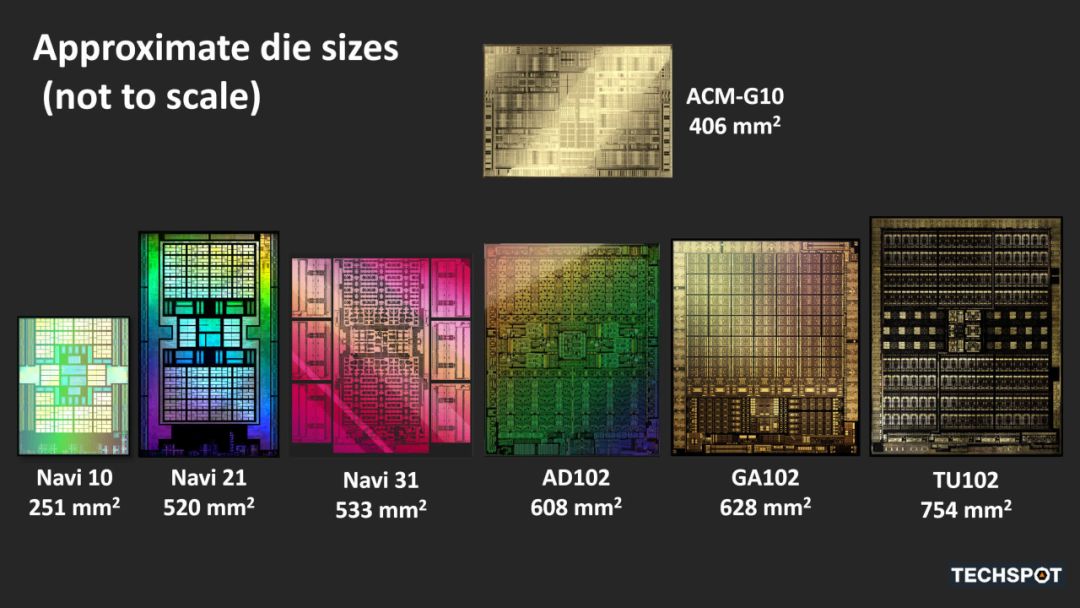

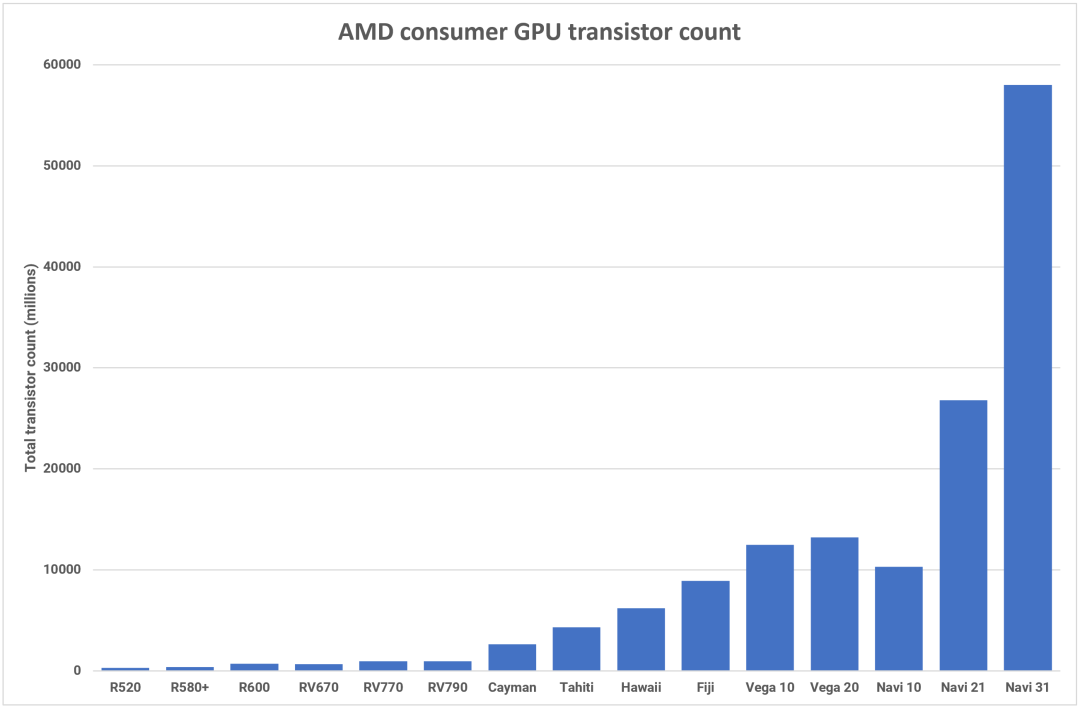

就芯片尺寸而言,GCD比Navi 21 小 42%,为 300 mm 2。每个 MCD 仅 37mm 2,因此 Navi 31 的组合芯片面积与其前身大致相同。AMD 仅公布了所有小芯片的晶体管总数,但这款新 GPU 数量达到 580 亿个,是他们有史以来“最大的”消费类图形处理器。

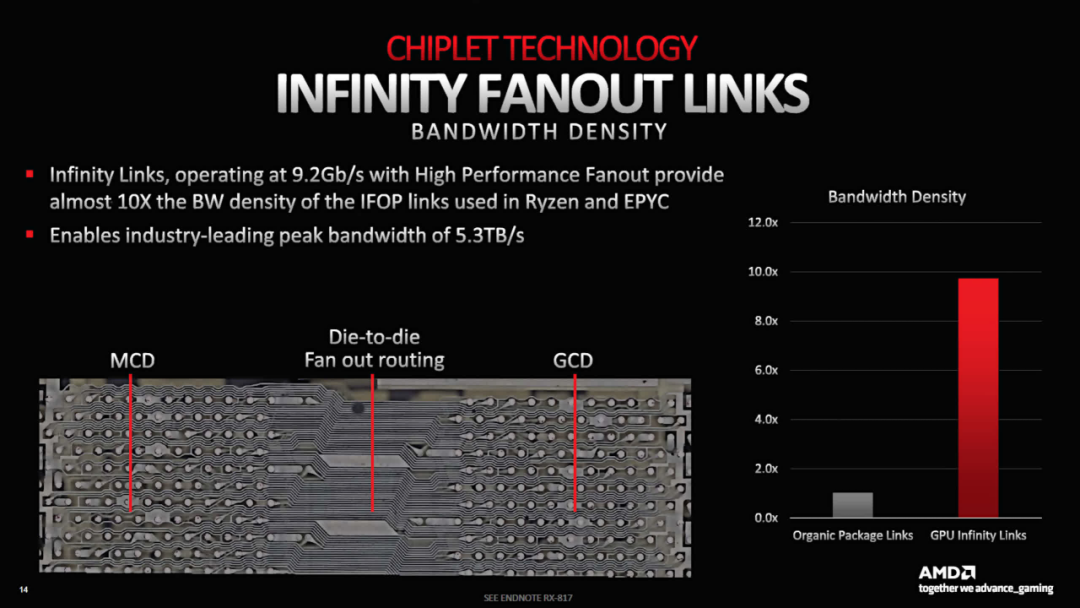

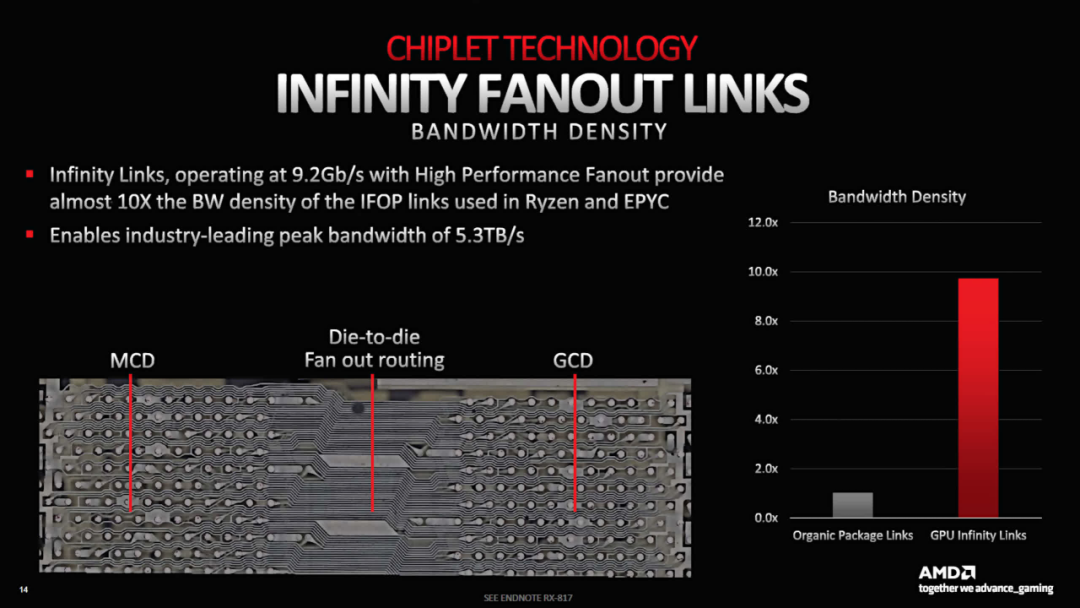

为了将每个 MCD 连接到 GCD,AMD 使用了所谓的高性能扇出——密集的走线,占用的空间非常小。Infinity Links(AMD 专有的互连和信号系统)运行速度高达 9.2Gb/s,每个 MCD 的链路宽度为 384 位,MCD 到 GCD 的带宽达到 883GB/s(双向)。

对于单个 MCD,这相当于高端显卡的全局内存带宽。Navi 31 中全部有 6 个,L2 到 MCD 的总带宽达到 5.3TB/s。

与传统的单片芯片相比,使用复杂的扇出意味着芯片封装的成本将会更高,但该工艺是可扩展的——不同的 SKU 可以使用相同的 GCD,但 MCD 的数量不同。较小尺寸的单个小芯片芯片应该会提高晶圆产量,但没有迹象表明 AMD 是否在 MCD 的设计中纳入了任何冗余。

如果没有,则意味着任何在 SRAM 中存在缺陷的小芯片,这些缺陷会导致内存阵列的该部分无法使用,那么它们将必须被分类用于低端型号 SKU,或者根本不使用。

AMD 迄今为止仅发布了两款 RDNA 3 显卡(Radeon RX 7900 XT 和 XTX),但在这两种型号中,MCD 均具有 16MB 缓存。如果下一轮 Radeon 卡配备 256 位内存总线和 64MB L3 缓存,那么它们也需要使用“完美”的 16MB 芯片。

然而,由于它们的面积非常小,单个 300mm 晶圆可能会产生超过 1500 个 MCD。即使其中 50% 必须报废,这仍然足以提供 125 个 Navi 31 封装。

我们还需要一段时间才能知道 AMD 的设计实际上具有多大的成本效益,但该公司现在和将来都完全致力于使用这种方法,尽管仅限于更大的 GPU。预算 RNDA 3 模型的缓存量要少得多,将继续使用单片制造方法,因为这种制造方法更具成本效益。

英特尔的ACM-G10处理器尺寸为406mm 2,晶体管总数为217亿个,在组件数量和芯片面积方面介于AMD的Navi 21和Nvidia的GA104之间。

这实际上使它成为一个相当大的处理器,这就是为什么英特尔选择 GPU 的市场领域似乎有些奇怪的原因。Arc A770显卡采用完整的 ACM-G10 芯片,与 Nvidia 的 GeForce RTX 3060等显卡进行竞争,后者使用的芯片尺寸和晶体管数量只有英特尔一半。

那么为什么它这么大呢?可能的原因有两个:16MB 的二级缓存和每个 XEC 中的矩阵单元数量非常多。采用前者的决定是合乎逻辑的,因为它减轻了全局内存带宽的压力,但后者很容易被认为对其销售的领域来说是过多的。RTX 3060 有 112 个 Tensor 核心,而 A770 有 512 个 XMX单元。

英特尔的另一个奇怪的选择是使用台积电 N6 来制造 Alchemist 芯片,而不是他们自己的工厂。关于此事的官方声明引用了成本、晶圆厂产能和芯片工作频率等因素。

这表明英特尔的同等生产设施(使用更名后的intel 7节点)将无法满足预期需求,其Alder和Raptor Lake CPU占据了大部分产能。

他们会将 CPU 输出的相对下降以及这对收入的影响与使用 Alchemist 获得的收益进行比较。简而言之,最好付钱给台积电制造新的 GPU。

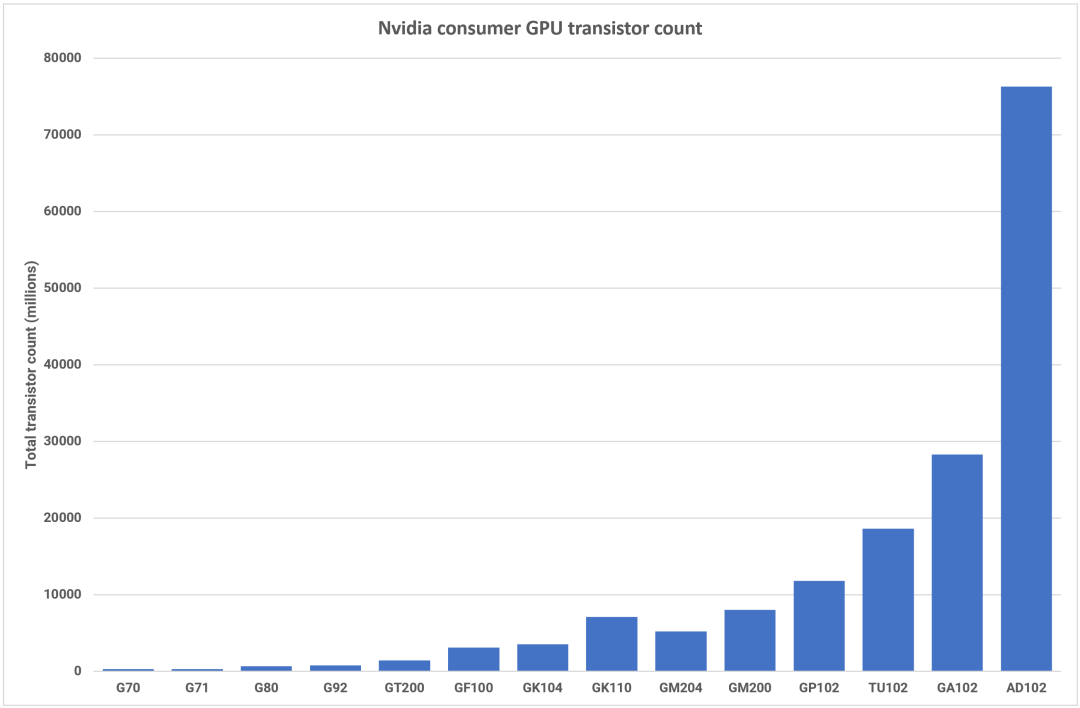

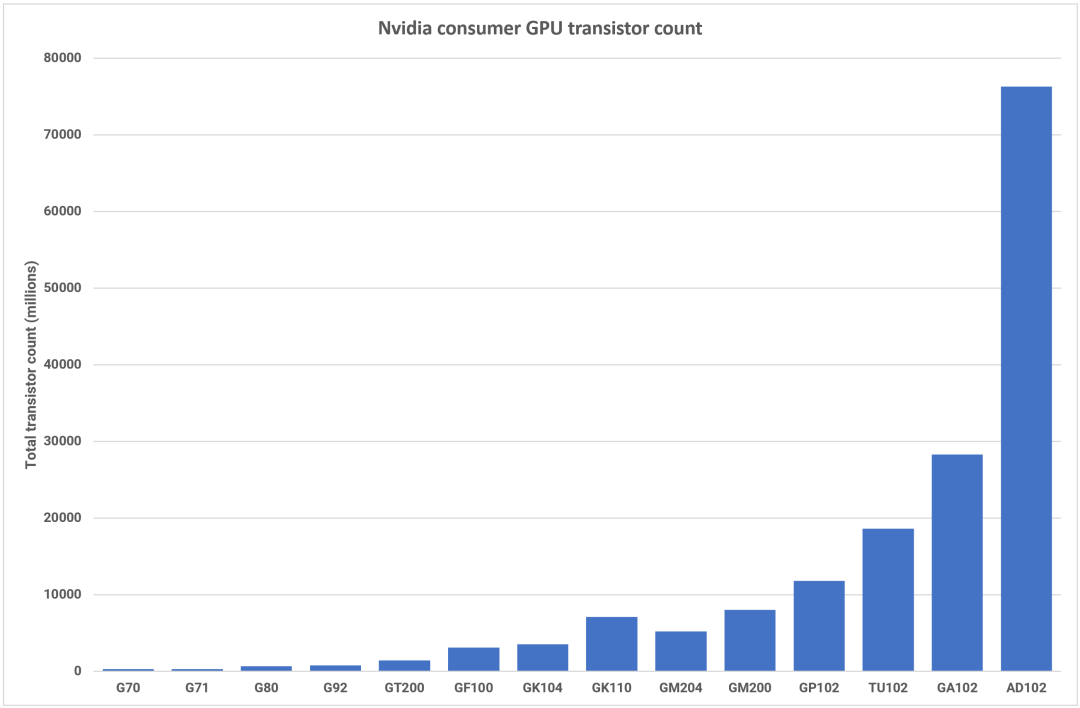

AMD 利用其多芯片专业知识并开发了用于制造大型 RDNA 3 GPU 的新技术,而 Nvidia 则坚持 Ada 系列的单片设计。GPU 公司在制造超大型处理器方面拥有丰富的经验,但 608mm2 的AD102 并不是其发布的物理上最大的芯片(这一荣誉颁给了826mm2的GA100)。然而,Nvidia 拥有 763 亿个晶体管,其组件数量远远领先于迄今为止任何消费级 GPU。

相比之下,GeForce RTX 3080 及更高版本中使用的 GA102 显得轻量级,只有 268 亿。这 187% 的增长得益于 SM 数量的 71% 增长和 L2 缓存数量的 1500% 的提升。

如此大而复杂的芯片总是难以实现完美的晶圆良率,这就是为什么之前的高端 Nvidia GPU 催生了众多 SKU。通常,随着新架构的推出,他们的专业显卡系列(例如 A 系列、Tesla 等)首先发布。

当 Ampere 发布时,GA102 出现在两款消费级卡中,并最终在 14 种不同的产品中找到了应用。到目前为止,Nvidia 仅选择在两款产品中使用 AD102:GeForce RTX 4090和RTX 6000。不过,后者自 9 月份出现以来一直无法购买。

RTX 4090 使用的芯片更接近分箱过程,禁用了 16 个 SM 和 24MB 二级缓存,而 RTX 6000 仅禁用了两个 SM。这就让人不禁要问:剩下的die在哪里?

但由于没有其他产品使用 AD102,我们只能假设 Nvidia 正在储备它们,尽管其他产品的用途尚不清楚。

GeForce RTX 4080使用 AD103,其尺寸为 379mm2和 459 亿个晶体管,与它的大哥完全不同——更小的芯片(80 个 SM、64MB 二级缓存)应该会带来更好的产量,但同样只有一种产品使用它。

他们还发布了另一款 RTX 4080,其中一款使用了较小的 AD104,但由于收到的批评而取消了发布。预计这款 GPU 现在将用于推出RTX 4070 系列。

Nvidia 显然拥有大量基于 Ada 架构构建的 GPU,但似乎也非常不愿意发货。造成这种情况的原因之一可能是他们正在等待安培驱动的显卡上架;另一个事实是,它主导了一般用户和工作站市场,并且可能认为它现在不需要提供任何其他东西。

但考虑到 AD102 和 103 提供的原始计算能力有了显着提高,Ada 专业卡的数量如此之少就有些令人费解了——该行业总是渴望更多的处理能力。

Superstar DJs: 显示和媒体引擎

当谈到 GPU 的媒体和显示引擎时,与 DirectX 12 功能或晶体管数量等方面相比,它们通常采用幕后营销方法。但随着游戏流媒体行业产生数十亿美元的收入,我们开始看到更多的努力来开发和推广新的显示功能。

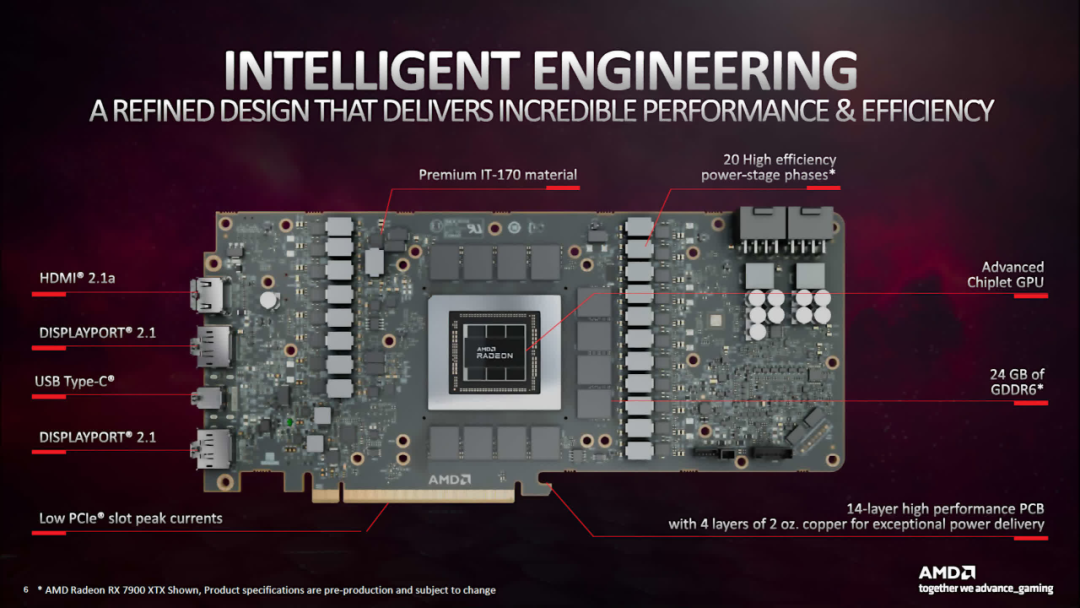

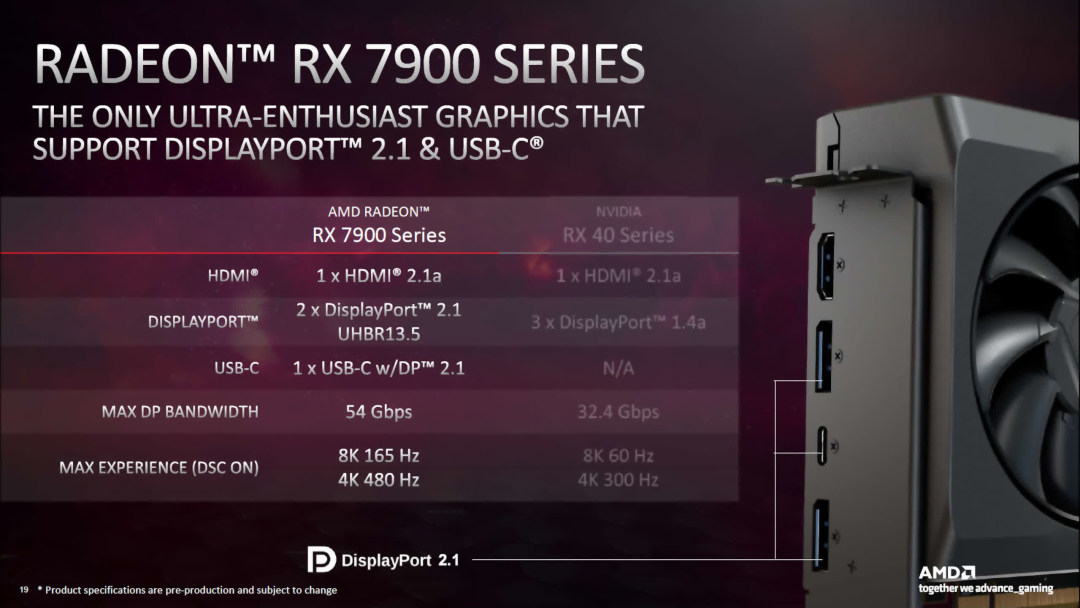

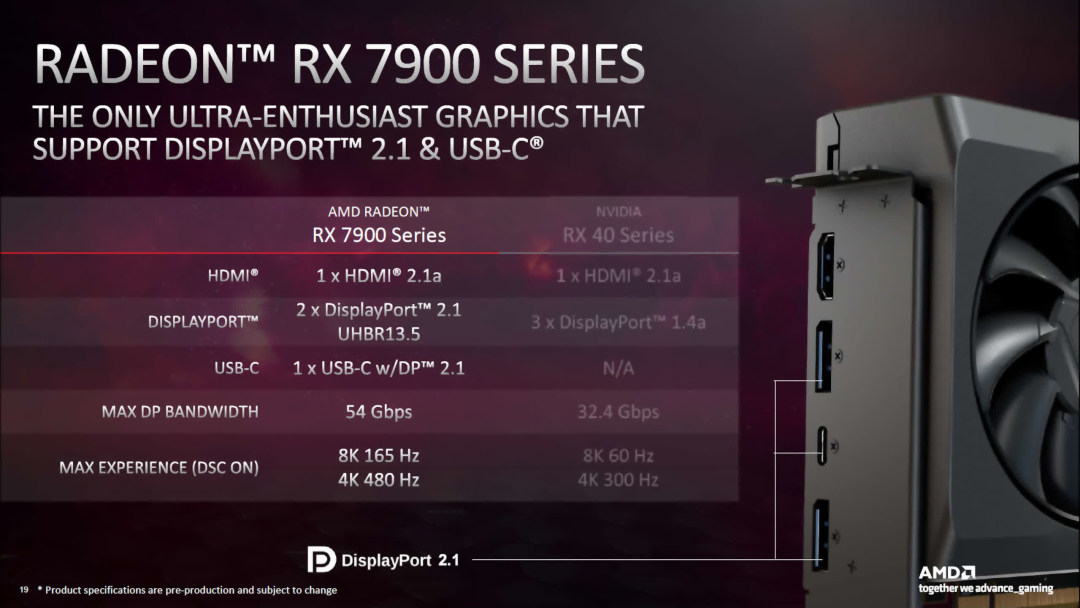

对于 RDNA 3,AMD 更新了许多组件,最值得注意的是对 DisplayPort 2.1 和 HDMI 2.1a 的支持。鉴于监督 DisplayPort 规范的组织 VESA在 2022 年底才发布 2.1 版本,GPU 供应商如此迅速地采用该系统是一个不寻常的举动。

新显示引擎支持的最快 DP 传输模式是 UHBR13.5,最大 4 通道传输速率为 54 Gbps。对于标准时序下 4K 分辨率、144Hz 刷新率、无任何压缩的情况来说,这已经足够了。

使用 DSC(显示流压缩:Display Stream Compression),DP2.1 连接允许高达 4K@480Hz 或 8K@165Hz - 比 RDNA 2 中使用的 DP1.4a 有了显著改进。

英特尔的 Alchemist 架构采用具有 DP 2.0(UHBR10,40 Gbps)和 HDMI 2.1 输出的显示引擎,尽管并非所有使用该芯片的 Arc 系列显卡都可以利用最大功能。

虽然ACM-G10并不针对高分辨率游戏,但采用最新的显示连接规格意味着可以在没有任何压缩的情况下使用电子竞技显示器(例如1080p、360Hz)。该芯片可能无法在此类游戏中呈现如此高的帧速率,但至少显示引擎可以。

AMD 和英特尔对 DP 和 HDMI 中快速传输模式的支持正是您对全新架构的期望,因此 Nvidia 选择不对 Ada Lovelace 这样做有点不协调。

AD102 对于所有晶体管(几乎与 Navi 31 和 ACM-G10 加在一起相同)仅具有具有 DP1.4a 和 HDMI 2.1 输出的显示引擎。对于 DSC,前者对于 4K@144Hz 来说已经足够好了,但是当竞争对手支持不压缩的情况下,这显然是错失机会。

GPU 中的媒体引擎负责视频流的编码和解码,所有三个供应商在其最新架构中都拥有丰富的功能集。

在 RDNA 3 中,AMD 添加了针对 AV1 格式的完整同步编码/解码(仅在之前的 RDNA 2 中进行解码)。关于新媒体引擎的信息并不多,只是它可以同时处理两个 H.264/H.265 流,并且 AV1 的最大速率为 8K@60Hz。AMD 还简要提到了“AI 增强”视频解码,但没有提供更多细节。

英特尔的 ACM-G10 具有类似的功能范围,可用于 AV1、H.264 和 H.265 的编码/解码,但与 RDNA 3 一样,细节非常少。对 Arc 桌面显卡中的首批 Alchemist 芯片的一些早期测试表明,媒体引擎至少与 AMD 和 Nvidia 在其先前架构中提供的媒体引擎一样好。

Ada Lovelace 也采用了 AV1 编码和解码,Nvidia 声称新系统的编码效率比 H.264 高 40%,表面上看,使用新格式时视频质量提高了 40%。

高端 GeForce RTX 40 系列显卡将配备配备两个 NVENC 编码器的 GPU,您可以选择以 60Hz 编码 8K HDR,或改进视频导出的并行化,每个编码器同时处理半帧。

GPU 的下一步是什么?

桌面 GPU 市场上已经有三个供应商了,很明显,每个供应商都有自己的图形处理器设计方法,尽管英特尔和 Nvidia 也采取了类似的思维方式。

对于他们来说,Ada 和 Alchemist 在某种程度上是万事通,可用于各种游戏、科学、媒体和数据工作负载。ACM-G10 中对矩阵和张量计算的高度重视以及不愿完全重新设计其 GPU 布局表明英特尔更倾向于科学和数据,而不是游戏,但考虑到这些领域的潜在增长,这是可以理解的。

对于最后三种架构,Nvidia 专注于改进已经很好的架构,并减少整体设计中的各种瓶颈,例如内部带宽和延迟。虽然 Ada 是对 Ampere 的自然改进(Nvidia 多年来一直遵循这一主题),但当你观察晶体管数量的绝对规模时,AD102 却显得异常进化。

与 GA102 相比,差异非常显着,但这种巨大的飞跃引发了许多问题。首先,对于 Nvidia 的最高端消费产品来说,AD103 是否是比 AD102 更好的选择?

与 RTX 4080 中使用的 AD103 相比,AD103 的性能比 RTX 3090 有了相当大的改进,并且与它的大哥一样,64MB 的二级缓存有助于抵消相对较窄的 256 位全局内存总线宽度。它的尺寸为 379mm2,比 GeForce RTX 3070 中使用的 GA104 小,因此制造利润比 AD102 高得多。它还包含与 GA102 相同数量的 SM,并且该芯片最终在 15 种不同的产品中得到了应用。

另一个值得问的问题是,Nvidia 在架构和制造方面将走向何方?他们能否在仍坚持使用单片芯片的情况下实现类似的缩放水平?

AMD 对 RDNA 3 的选择凸显了竞争的潜在路线。通过将芯片中规模最差的部分(在新工艺节点中)转移到单独的小芯片中,AMD 已经能够成功地延续 RDNA 和 RDNA 2 之间的大型制造和设计飞跃。

虽然它不像 Nvidia 的 AD102 那么大,但 AMD Navi 31 的硅片价值仍然高达 580 亿个晶体管,是 Navi 21 的两倍多,也是我们最初的 RDNA GPU Navi 10 的 5 倍多(尽管这不是 Navi 21 的两倍)。

AMD 和 Nvidia 的成就并不是孤立取得的。GPU 晶体管数量如此大幅增加的唯一原因是台积电和三星之间作为半导体设备主要制造商的激烈竞争。两者都致力于提高逻辑电路的晶体管密度,同时继续降低功耗。台积电对于当前的节点改进及其下一步的主要工艺有明确的路线图。

目前尚不清楚 Nvidia 是否会效仿 AMD 的做法,并在 Ada 的继任者中采用小芯片布局,但接下来的一两年可能会起到决定性作用。如果 RDNA 3 被证明在财务上取得了成功,无论是在收入还是总出货量方面,那么 Nvidia 很可能会效仿。

然而,第一个使用 Ampere 架构的芯片是 GA100——一款数据中心 GPU,尺寸为829mm2 ,拥有 542 亿个晶体管。它由 TSMC 使用其 N7 节点制造(与 RDNA 和大多数 RDNA 2 系列相同)。使用 N4 来制造 AD102,使得 Nvidia 能够设计出晶体管密度几乎是其前身的两倍的 GPU。

在下一个架构中使用 N2 可以实现这一目标吗?有可能,但缓存的大幅增长(扩展性非常差)表明,即使台积电在未来的节点上取得了一些引人注目的成绩,控制 GPU 大小也将变得越来越困难。

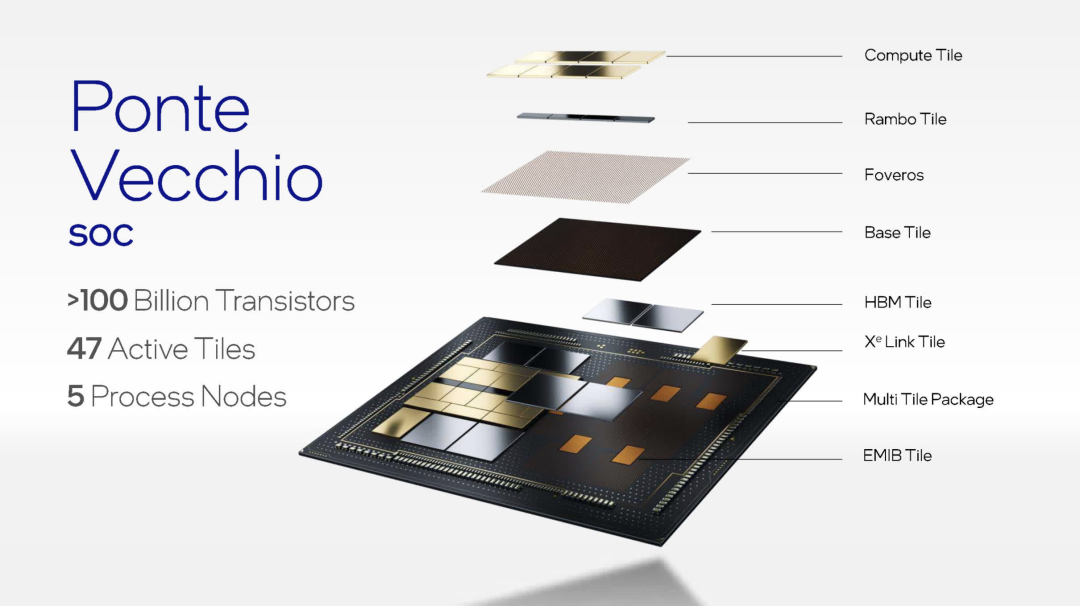

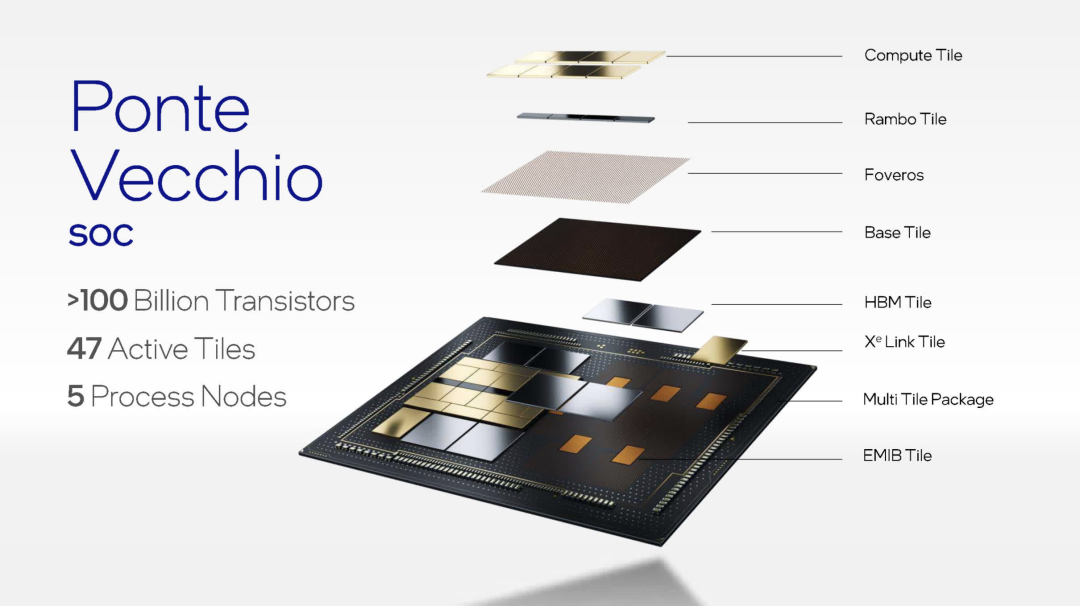

英特尔已经在使用小芯片,但仅限于其巨大的Ponte Vecchio数据中心 GPU。由47块不同的tiles组成,当中有些是台积电制造的,有些是英特尔自己制造的,其参数相当高。例如,完整的双 GPU 配置拥有超过 1000 亿个晶体管,这使得 AMD 的 Navi 31 看起来非常“小”。当然,它不适用于任何类型的台式电脑,严格来说也“不仅仅是”GPU——这是一个数据中心处理器,重点关注矩阵和张量工作负载。

在转向“Xe Next”之前,其 Xe-HPG 架构至少还要进行两次修订,我们很可能会在英特尔消费类显卡中看到平铺的使用。

不过,目前,我们将让 Ada 和 Alchemist 使用传统的单片芯片,而 AMD 则将混合芯片系统用于中高端卡,并为其预算 SKU 使用单芯片。

到本世纪末,我们可能会看到几乎所有类型的图形处理器,它们都是由精选的不同tile和小芯片构建而成,全部使用各种工艺节点制成。GPU 仍然是台式电脑中最引人注目的工程壮举之一——晶体管数量没有显示出增长放缓的迹象,而今天普通显卡的计算能力在大约 10 年前只能是梦想。

让我们进入下一场三向架构之战吧!

在 GPU 领域,2022 年无论好坏都是一个重要的里程碑。英特尔兑现了重新进入独立显卡市场的承诺,Nvidia将显卡尺寸和价格推向了顶峰,AMD将 CPU 技术带入了显卡领域。

围绕 GPU 的热情弥漫在在线论坛中,让 PC 爱好者对显卡市场的转变感到既敬畏又震惊。在这种喧嚣中,人们很容易忘记最新的产品配备了家用电脑中最复杂、最强大的芯片。

在本文中,我们将深入探讨他们的架构。让我们剥开层层,看看有什么新内容、它们有什么共同点,以及这些对普通用户意味着什么。

GPU整体结构:从上到下

让我们从本文的一个重要方面开始——这不是性能比较。相反,我们正在研究 GPU 内部的所有内容是如何排列的,检查规格和数据,以了解 AMD、英特尔和 Nvidia 在设计图形处理器时所采用的方法差异。

我们将首先了解使用我们正在研究的架构的最大可用芯片的整体 GPU 组成。需要强调的是,英特尔的产品并不针对与 AMD 或 Nvidia 相同的市场,因为它在很大程度上是一款中档图形处理器。

这三者的尺寸不仅彼此不同,而且与使用先前架构的类似芯片也有很大不同。所有这些分析纯粹是为了了解这三个处理器的底层到底是什么。在分解每个 GPU 的基本部分(着色器核心、光线追踪功能、内存层次结构以及显示和媒体引擎)之前,我们将检查整体结构。

一、AMD Navi 31

按字母顺序排列,第一个出现的是 AMD 的 Navi 31,这是他们迄今为止发布的最大的 RDNA 3 芯片。与 Navi 21 相比,我们可以看到他们之前的高端 GPU 的组件数量明显增长......

着色器引擎 (SE:Shader Engines) 容纳的计算单元 (CU:Compute Units) 较少,为 16 个,而不是 200 个,但现在总共有 6 个 SE,比以前多了两个。这意味着Navi 31拥有多达96个CU,总共配备6144个流处理器(SP:Stream Processors)。AMD 已经对 RDNA 3 的 SP 进行了全面升级,我们将在后面讨论。

每个着色器引擎还包含一个处理光栅化( rasterization)的专用单元、一个用于三角形( triangle )设置的图元引擎(primitive engine )、32 个渲染输出单元 (ROP:render output units) 和两个 256kB L1 缓存。最后一个方面现在大小增加了一倍,但每个 SE 的 ROP 计数仍然相同。

AMD 也没有对光栅器( rasterizer )和原始引擎(primitive engines)进行太大改变——所称的 50% 改进是针对整个芯片进行的,因为它的 SE 比 Navi 21 芯片多了 50%。然而,SE 处理指令的方式发生了变化,例如更快地处理多个绘制命令(multiple draw commands)和更好地管理管道阶段( pipeline stages),这应该会减少 CU 在继续执行另一个任务之前需要等待的时间。

最明显的变化是在 11 月发布之前引起最多谣言和八卦的变化——GPU 封装的小芯片方法。凭借在该领域多年的经验,AMD 选择这样做在某种程度上是合乎逻辑的,但这完全是出于成本/制造原因,而不是性能。

我们将在本文后面更详细地讨论这一点,所以现在我们只关注哪些部分在哪里。在 Navi 31 中,最终层缓存的内存控制器及其相关分区位于主处理器(GCD,Graphics Compute Die)周围的单独小芯片(称为 MCD 或Memory Cache Dies)中。

由于需要提供更多数量的 SE,AMD 也将 MC 数量增加了 50%,因此 GDDR6 全局内存的总总线宽度现在为 384 位。这次 Infinity Cache 总量减少了(96MB vs 128MB),但更大的内存带宽抵消了这一点。

二、英特尔ACM-G10

接下来是 Intel 和 ACM-G10 芯片(以前称为 DG2-512)。虽然这不是英特尔生产的最大的 GPU,但它是他们最大的消费类图形芯片。

该框图是相当标准的排列,尽管看起来更类似于 Nvidia 的而不是 AMD 的。共有 8 个渲染切片(Render Slices),每个渲染切片包含 4 个 Xe 核心,总共 512 个矢量引擎(Vector Engines:相当于 AMD 的流处理器和 Nvidia 的 CUDA 核心 )。

每个渲染切片中还包含一个基元单元、光栅器、深度缓冲处理器、32 个纹理单元和 16 个 ROP。乍一看,这款 GPU 似乎相当大,因为 256 个 TMU 和 128 个 ROP 比 Radeon RX 6800 或 GeForce RTX 2080 中的数量还要多。

然而,AMD 的 RNDA 3 芯片拥有 96 个计算单元,每个计算单元有 128 个 ALU,而 ACM-G10 总共有 32 个 Xe 核心,每个核心有 128 个 ALU。因此,仅就 ALU 数量而言,英特尔 Alchemist 驱动的 GPU 的大小是 AMD 的三分之一。但正如我们稍后将看到的,ACM-G10 的大部分芯片都交给了不同的数字处理单元。

与英特尔通过 OEM 供应商发布的首款 Alchemist GPU相比,该芯片在组件数量和结构排列方面具备成熟架构的所有特征。

三、英伟达AD102

我们完成了对 Nvidia AD102 不同布局的开场概述,这是他们第一个使用 Ada Lovelace 架构的 GPU。与它的前身Ampere GA102相比,它看起来并没有什么不同,只是大了很多。就所有意图和目的而言,确实如此。

Nvidia 使用图形处理集群 (GPU:Graphics Processing Cluster) 的组件层次结构,其中包含 6 个纹理处理集群 (TPC:Texture Processing Clusters),每个集群包含 2 个流式多处理器 (SM)。这种安排对于Ada来说并没有改变,但总数肯定已经改变了……

在完整的 AD102 芯片中,GPC 数量从 7 个增加到 12 个,因此现在总共有 144 个 SM,总共有 18432 个 CUDA 核心。与 Navi 31 中的 6144 个 SP 相比,这个数字似乎高得离谱,但 AMD 和 Nvidia 对其组件的计数方式不同。

虽然这大大简化了问题,但 1 个 Nvidia SM 相当于 1 个 AMD CU——两者都包含 128 个 ALU。因此,Navi 31 的尺寸是英特尔 ACM-G10 的两倍(仅 ALU 数量),而 AD102 的尺寸是英特尔 ACM-G10 的 3.5 倍。

这就是为什么当芯片在规模上有如此明显的差异时,对它们进行任何直接的性能比较是不公平的。然而,一旦它们进入显卡、定价并上市,那么情况就不同了。

但我们可以比较的是三个处理器中最小的重复部分。

着色器核心(Shader Cores):

走进 GPU 的大脑

从整个处理器的概述开始,现在让我们深入了解芯片的核心,看看处理器的基本数字处理部分:着色器核心。

这三个制造商在描述他们的芯片时使用不同的术语和短语,特别是在概述图时。因此,在本文中,我们将使用我们自己的图像,具有常见的颜色和结构,以便更容易看出相同和不同之处。

一、AMD RDNA 3

AMD GPU 着色部分内最小的统一结构称为双计算单元(DCU:Double Compute Unit)。在某些文档中,它仍然称为工作组处理器 (WGP:Workgroup Processor),而其他文档则将其称为计算单元对(CUP:Compute Unit Pair)。

请注意,如果这些图中未显示某些内容(例如常量缓存、双精度单元),并不意味着它们不存在于体系结构中。

在很多方面,整体布局和结构元素与 RDNA 2 相比并没有太大变化。两个计算单元共享一些缓存和内存,每个计算单元包含两组 32 个流处理器 (SP)。

第 3 版的新增功能是,每个 SP 现在容纳的算术逻辑单元 (ALU:arithmetic logic units ) 数量是以前的两倍。现在,每个 CU 有两组 SIMD64 单元,每个组有两个数据端口——一个用于浮点、整数和矩阵运算,另一个仅用于浮点和矩阵运算。

AMD 确实针对不同的数据格式使用单独的 SP, RDNA 3 中的计算单元支持使用 FP16、BF16、FP32、FP64、INT4、INT8、INT16 和 INT32 值进行操作。

使用 SIMD64 意味着每个线程调度程序可以在每个时钟周期发出一组 64 个线程(称为wavefront),或者可以共同发出两个 32 个线程的波前。AMD 保留了与以前的 RDNA 架构相同的指令规则,因此这是由 GPU/驱动程序处理的。

另一个重要的新功能是 AMD 所谓的 AI 矩阵加速器的出现。

与我们很快就会看到的 Intel 和 Nvidia 的架构不同,它们并不充当单独的单元——所有矩阵运算都利用 SIMD 单元,并且任何此类计算(称为波矩阵乘法累加,WMMA:Wave Matrix Multiply Accumulate)都将使用完整的 64 个 ALU 组。

在撰写本文时,人工智能加速器的确切性质尚不清楚,但它可能只是与处理指令和涉及的大量数据相关的电路,以确保最大吞吐量。它很可能与 Nvidia 的Hopper 架构中的张量内存加速器具有类似的功能。

与 RDNA 2 相比,变化相对较小——较旧的架构还可以处理 64 个线程波前(又名 Wave64),但这些是在两个周期内发布的,并且在每个计算单元中使用两个 SIMD32 块。现在,这一切都可以在一个周期内完成,并且仅使用一个 SIMD 块。

在之前的文档中,AMD 表示 Wave32 通常用于计算和顶点着色器(也可能用于光线着色器),而 Wave 64 主要用于像素着色器,驱动程序会相应地编译着色器。因此,转向单周期 Wave64 指令问题将为严重依赖像素着色器的游戏带来推动。

然而,所有这些额外的可用功率都需要正确利用才能充分利用。所有 GPU 架构都是如此,并且它们都需要大量线程负载,才能做到这一点(这也有助于隐藏与 DRAM 相关的固有延迟)。

因此,随着 ALU 数量增加一倍,AMD 推动了程序员尽可能使用指令级并行性的需求。这在图形领域并不是什么新鲜事,但 RDNA 相对于 AMD 旧的 GCN 架构的一个显著优势是,它不需要那么多的运行线程来达到充分利用。鉴于现代渲染在游戏中变得多么复杂,开发人员在编写着色器代码时需要做更多的工作。

二、Intel Alchemist

现在让我们转向英特尔,看看 Alchemist 架构中的 DCU 等效项,称为Xe Core(我们将其缩写为 XEC)。乍一看,与 AMD 的结构相比,这些看起来绝对是巨大的。

RDNA 3 中的单个 DCU 包含四个 SIMD64 块,而英特尔的 XEC 包含16 个SIMD8 单元,每个单元都由自己的线程调度程序和调度系统管理。与 AMD 的流处理器一样,Alchemist 中所谓的矢量引擎可以处理整数和浮点数据格式。不支持 FP64,但这在游戏中不是什么大问题。

英特尔一直使用相对较窄的 SIMD——Gen11 中使用的 SIMD 仅为 4 宽(即同时处理 4 个线程),而 Gen 12 的宽度仅加倍(例如,在其 Rocket Lake CPU 中使用)。

但考虑到游戏行业已经使用 SIMD32 GPU 多年,因此游戏也进行了相应的编码,因此保留狭窄执行块的决定似乎会适得其反。

AMD 的 RDNA 3 和 Nvidia 的 Ada Lovelace 的处理块可以在一个周期内发出 64 或 32 个线程,而英特尔的架构需要 4 个周期才能在一个 VE 上实现相同的结果,因此每个 XEC 有 16 个 SIMD 单元。

然而,这意味着如果游戏的编码方式不能确保 VE 被完全占用,SIMD 和相关资源(缓存、带宽等)将处于闲置状态。英特尔Arc 系列显卡的基准测试结果的一个共同主题是,它们往往在更高的分辨率和/或具有大量复杂的现代着色器例程的游戏中表现更好。

这在一定程度上是由于单位细分和资源共享程度较高。Chips and Cheese网站的微基准分析表明,尽管拥有丰富的 ALU,该架构仍难以实现适当的利用。

转到 XEC 的其他方面,尚不清楚 0 级指令缓存有多大,但 AMD 的指令缓存是 4 路(因为它服务于四个 SIMD 块),而 Intel 的缓存必须是 16 路,这增加了复杂性缓存系统的。

英特尔还选择为处理器提供用于矩阵运算的专用单元,每个向量引擎对应一个单元。拥有如此多的单元意味着芯片的很大一部分专门用于处理矩阵数学。

AMD 使用 DCU 的 SIMD 单元来完成此操作,而 Nvidia 每个 SM 有四个相对较大的张量/矩阵单元,而英特尔的方法似乎有点过分,因为他们有一个单独的架构,称为 X e-HP,用于计算应用程序。

另一个奇怪的设计似乎是处理块中的加载/存储(LD/ST)单元。我们的图表中未显示,它们管理来自线程的内存指令,在寄存器文件和 L1 缓存之间移动数据。Ada Lovelace 与 Ampere 相同,每个 SM 分区有 4 个,总共 16 个。RDNA 3 也与其前身相同,每个 CU 都有专用的 LD/ST 电路作为纹理单元的一部分。

英特尔的 Xe-HPG 演示显示每个 XEC 仅一个 LD/ST,但实际上,它内部可能由更多分立单元组成。然而,在他们的OneAPI优化指南中,一张图表表明 LD/ST 一次循环一个单独的寄存器文件。如果是这种情况,那么 Alchemist 将始终难以实现最大缓存带宽效率,因为并非所有文件都同时得到服务。

三、Nvidia Ada Lovelace

最后一个需要关注的处理模块是 Nvidia 的流式多处理器(SM:Streaming Multiprocessor ) – DCU/XEC 的 GeForce 版本。这个结构与2018年的图灵架构相比并没有太大的改变。事实上,它几乎与Ampere相同。

一些单元已经过调整以提高其性能或功能集,但在大多数情况下,没有太多新的东西可以谈论。事实上,可能有,但众所周知,英伟达不愿透露太多有关其芯片的内部操作和规格的信息。英特尔提供了更多细节,但这些信息通常隐藏在其他文档中。

但总结一下结构,SM 分为四个分区。每个处理器都有自己的 L0 指令缓存、线程调度程序和分派单元,以及与 SIMD32 处理器配对的 64 kB 寄存器文件部分。

正如AMD的RDNA 3一样,SM支持双发出指令,其中每个分区可以同时处理两个线程,一个使用FP32指令,另一个使用FP32或INT32指令。

Nvidia 的 Tensor 核心现已进入第四版,但这一次,唯一显著的变化是包含了Hopper 芯片中的FP8 Transformer 引擎,原始吞吐量数据保持不变。

低精度浮点格式的加入意味着GPU应该更适合AI训练模型。Tensor 核心还提供Ampere 的稀疏功能,可提供高达两倍的吞吐量。

另一个改进在于光流加速器 (OFA:Optical Flow Accelerator) 引擎(图中未显示)。该电路生成光流场( optical flow field),用作DLSS算法的一部分。OFA 的安培性能提高了一倍,额外的吞吐量被用在最新版本的临时抗锯齿升频器 DLSS 3 中。

DLSS 3已经面临相当多的批评,主要集中在两个方面:DLSS 生成的帧不是“真实的”,并且该过程给渲染链增加了额外的延迟。第一个并不是完全无效,因为系统的工作原理是首先让 GPU 渲染两个连续的帧,将它们存储在内存中,然后使用神经网络算法确定中间帧的样子。

然后,当前链返回到第一个渲染帧并显示该帧,然后是 DLSS 帧,然后是渲染的第二帧。由于游戏引擎尚未在中帧循环,因此屏幕会在没有任何潜在输入的情况下刷新。而且由于需要停止而不是呈现两个连续的帧,因此为这些帧轮询的任何输入也将停止。

DLSS 3 是否会变得流行或普遍还有待观察。

尽管 Ada 的 SM 与 Ampere 非常相似,但 RT 内核有显着的变化,我们将很快解决这些变化。现在我们来总结一下AMD、Intel、Nvidia的GPU重复结构的计算能力。

处理块比较

我们可以通过查看每个时钟周期的标准数据格式的操作数量来比较 SM、XEC 和 DCU 的功能。请注意,这些是峰值数字,实际上不一定可以实现。

Nvidia 的数字与 Ampere 相比没有变化,而 RDNA 3 的数字在某些领域增加了一倍。然而,Alchemist在矩阵运算方面处于另一个水平,尽管应该再次强调这些是峰值理论值的事实。

鉴于英特尔的图形部门像英伟达一样严重依赖数据中心和计算,因此看到该架构将如此多的芯片空间用于矩阵运算也就不足为奇了。缺乏 FP64 功能并不是问题,因为该数据格式并未真正用于游戏,并且该功能存在于其 X e -HP 架构中。

理论上,在矩阵/张量运算方面,Ada Lovelace 和 Alchemist 比 RDNA 3 更强,但由于我们正在研究主要用于游戏工作负载的 GPU,因此专用单元大多只是为 DLSS 和相关算法提供加速。XeSS——它们使用卷积自动编码器神经网络(CAENN)来扫描图像中的伪影并进行纠正。

AMD 的时间升级器(FidelityFX Super Resolution, FSR))不使用 CAENN,因为它主要基于Lanczos 重采样方法,然后是通过 DCU 处理的许多图像校正例程。然而,在RDNA 3 的发布中,简要介绍了FSR 的下一版本,并引用了一项名为“Fluid Motion Frames”的新功能。FSR 2.0 的性能提升高达两倍,普遍的共识是这可能涉及帧生成,如 DLSS 3 中那样,但这是否涉及任何矩阵运算尚不清楚。

适合每个人的光线追踪

随着使用 Alchemist 架构的 Arc 显卡系列的推出,英特尔与 AMD 和 Nvidia 一起提供 GPU,为图形中使用光线追踪所涉及的各种算法提供专用加速器。Ada 和 RNDA 3 都包含显着更新的 RT 单元,因此了解一下新的和不同的内容是有意义的。

从 AMD 开始,其光纤加速器的最大变化是添加硬件以改进包围体层次结构(BVH:bounding volume hierarchies)的遍历(traversal)。这些数据结构用于加速确定 3D 世界中光线照射到的表面。

在 RDNA 2 中,所有这些工作都是通过计算单元处理的,并且在某种程度上仍然如此。然而,对于 DXR(微软的光线追踪 API)来说,有对光线标志管理的硬件支持。

使用这些可以大大减少需要遍历 BVH 的次数,从而减少缓存带宽和计算单元的总体负载。本质上,AMD 专注于提高他们在之前架构中引入的系统的整体效率。

此外,硬件已更新,以改进盒子排序(box sorting,这使得遍历更快)和剔除算法(culling algorithms,以跳过测试空盒子)。再加上缓存系统的改进,AMD 表示,在相同的时钟速度下,与 RDNA 2 相比,光线追踪性能提高了 80%。

然而,这种改进并不能转化为使用光线追踪的游戏中每秒帧数增加 80% ,这些情况下的性能受到许多因素的影响,RT 单元的功能只是其中之一。

由于英特尔是光线追踪技术的新手,因此没有任何改进。相反,我们只是被告知他们的 RT 单元处理射线和三角形之间的 BVH 遍历和相交计算。这使得它们比 AMD 的系统更类似于 Nvidia 的系统,但关于它们的信息并不多。

但我们确实知道每个 RT 单元都有一个未指定大小的缓存用于存储 BVH 数据,以及一个单独的单元用于分析和排序光线着色器线程,以提高 SIMD 利用率。

每个 XEC 与一个 RT 单元配对,每个渲染切片总共有四个。在游戏中启用光线追踪的A770 的一些早期测试表明,无论英特尔采用何种结构,Alchemist 的光线追踪整体能力至少与 Ampere 芯片一样好,并且比 RDNA 2 型号稍好一些。

但让我们再次重申,光线追踪也给着色核心、缓存系统和内存带宽带来了沉重压力,因此不可能从此类基准测试中提取 RT 单元性能。

对于 Ada Lovelace 架构,Nvidia 做出了许多改变,与 Ampere 相比,其性能提升幅度相当大。据称,用于射线-三角形相交计算的加速器的吞吐量提高了一倍,并且现在据说非不透明表面的 BVH 遍历速度提高了一倍。后者对于使用带有 alpha channel (透明度)的纹理的对象很重要,例如树上的叶子。

光线击中此类表面的完全透明部分不应导致击中结果——光线应直接穿过。然而,为了在当前使用光线追踪的游戏中准确确定这一点,需要处理多个其他着色器。Nvidia 的新不透明度微贴图引擎将这些表面分解成更多的三角形,然后确定到底发生了什么,从而减少了所需的光线着色器的数量。

Ada 光线追踪功能的另外两个附加功能是减少 BVH 的构建时间和内存占用(声称速度分别加快 10 倍和缩小 20 倍),以及为光线着色器重新排序线程的结构,从而提高效率。然而,前者不需要开发人员对软件进行任何更改,而后者目前只能通过 Nvidia 的 API 访问,因此对当前的 DirectX 12 游戏没有任何好处。

当我们测试 GeForce RTX 4090 的光线追踪性能时,启用光线追踪后帧速率的平均下降略低于 45%。使用 Ampere 驱动的 GeForce RTX 3090 Ti 时,下降了 56%。然而,这种改进不能完全归因于 RT 核心的改进,因为 4090 比以前的型号具有更多的着色吞吐量和缓存。

我们还没有看到 RDNA 3 的光线追踪改进会产生什么样的差异,但值得注意的是,没有一家 GPU 制造商期望单独使用 RT – 即仍然需要使用升级来实现高帧速率。

光线追踪的粉丝可能会有些失望,因为新一轮的图形处理器在这一领域没有取得任何重大进展,但自 2018 年 Nvidia 图灵架构首次出现以来,已经取得了很多进展。

内存:沿着数据高速公路行驶

GPU 处理数据的方式与其他芯片不同,而让 ALU 保持数据输入对其性能至关重要。在 PC 图形处理器的早期,内部几乎没有任何缓存,全局内存(整个芯片使用的 RAM)是非常慢的 DRAM。即使就在10年前,情况也没有好多少。

因此,让我们从 AMD 新架构中的内存层次结构开始,深入了解当前的情况。自第一次迭代以来,RDNA 使用了复杂的多级内存层次结构。最大的变化发生在一年前,当时 GPU 中添加了大量的 L3 缓存,在某些型号中高达 128MB。

第三轮的情况仍然如此,但有一些微妙的变化。

Nvidia 保留了与 Ampere 中使用的相同的内存结构,每个 SM 具有 128kB 的缓存,充当 L1 数据存储、共享内存和纹理缓存。可用于不同角色的数量是动态分配的。目前尚未提及 L1 带宽的任何变化,但在 Ampere 中,每个 SM 每个时钟周期为 128 字节。Nvidia 从未明确明确这一数字是累积的、结合读写的,还是仅针对一个方向的。

如果 Ada 至少与 Ampere 相同,那么所有 SM 的总 L1 带宽将达到每个时钟 18 kB,远大于 RDNA 2 和 Alchemist。

但必须再次强调的是,这些芯片不具有直接可比性,因为英特尔的芯片是作为中端产品定价和销售的,而 AMD 已明确表示Navi 31 的设计目的从来不是为了与 Nvidia 的 AD102 竞争。它的竞争对手是 AD103,它比 AD102 小得多。

内存层次结构的最大变化是,在完整的 AD102 芯片中,L2 缓存已增加到 96MB,是其前身 GA102 的 16 倍。与英特尔的系统一样,L2 进行分区并与 32 位 GDDR6X 内存控制器配对,以实现高达 384 位的 DRAM 总线宽度。

较大的缓存通常比较小的缓存具有更长的延迟,但由于时钟速度的提高和总线的一些改进,Ada Lovelace 显示出比 Ampere更好的缓存性能。

如果我们比较所有三个系统,英特尔和 Nvidia 对 L1 缓存采取相同的方法 -——它可以用作只读数据缓存或计算共享内存。对于后者,需要通过软件明确指示 GPU 以这种格式使用它,并且数据仅在使用它的线程处于活动状态时保留。这增加了系统的复杂性,但对计算性能产生了有用的提升。

在 RDNA 3 中,“L1”数据缓存和共享内存被分为两个 32kB L0 矢量缓存和一个 128kB 本地数据共享。AMD 所谓的 L1 缓存实际上是一组四个 DCU 和 L2 缓存之间用于只读数据的共享垫脚石(shared stepping stone)。

虽然缓存带宽没有 Nvidia 的那么高,但多层方法有助于解决这个问题,尤其是在 DCU 未得到充分利用的情况下。

巨大的处理器范围的缓存系统通常不是 GPU 的最佳选择,这就是为什么我们在以前的架构中没有看到超过 4 或 6MB 的缓存系统,但 AMD、Intel 和 Nvidia 都在最后一层是应对 DRAM 速度增长相对不足的问题。

向 GPU 添加大量内存控制器可以提供充足的带宽,但代价是芯片尺寸增加和制造费用增加,而 HBM3 等替代方案的使用成本要高得多。

我们还没有看到 AMD 的系统最终表现如何,但他们在 RDNA 2 中的四层方法在与 Ampere 的对抗中表现良好,并且比英特尔的系统要好得多。然而,随着 Ada 加入了更多的 L2,竞争不再那么简单。

芯片封装和工艺节点:建造的不同方式

AMD、英特尔和 Nvidia 有一个共同点——他们都使用台积电来制造 GPU。

AMD在Navi 31中的GCD和MCD使用了两种不同的节点,前者使用N5节点,后者使用N6(N7的增强版本)。英特尔还在其所有 Alchemist 芯片中使用 N6。在 Ampere 中,Nvidia 使用了三星旧的 8nm 工艺,但在 Ada 中,他们转回台积电及其 N4 工艺,这是 N5 的变体。

N4 拥有所有节点中最高的晶体管密度和最佳的性能功耗比,但当 AMD 推出 RDNA 3 时,他们强调只有逻辑电路的密度出现了显着增加。

SRAM(用于高速缓存)和模拟系统(用于存储器、系统和其他信号电路)微缩相对较小。再加上新工艺节点每晶圆价格的上涨,AMD 决定使用稍旧且更便宜的 N6 来制造 MCD,因为这些小芯片主要是 SRAM 和 I/O。

就芯片尺寸而言,GCD比Navi 21 小 42%,为 300 mm 2。每个 MCD 仅 37mm 2,因此 Navi 31 的组合芯片面积与其前身大致相同。AMD 仅公布了所有小芯片的晶体管总数,但这款新 GPU 数量达到 580 亿个,是他们有史以来“最大的”消费类图形处理器。

为了将每个 MCD 连接到 GCD,AMD 使用了所谓的高性能扇出——密集的走线,占用的空间非常小。Infinity Links(AMD 专有的互连和信号系统)运行速度高达 9.2Gb/s,每个 MCD 的链路宽度为 384 位,MCD 到 GCD 的带宽达到 883GB/s(双向)。

对于单个 MCD,这相当于高端显卡的全局内存带宽。Navi 31 中全部有 6 个,L2 到 MCD 的总带宽达到 5.3TB/s。

与传统的单片芯片相比,使用复杂的扇出意味着芯片封装的成本将会更高,但该工艺是可扩展的——不同的 SKU 可以使用相同的 GCD,但 MCD 的数量不同。较小尺寸的单个小芯片芯片应该会提高晶圆产量,但没有迹象表明 AMD 是否在 MCD 的设计中纳入了任何冗余。

如果没有,则意味着任何在 SRAM 中存在缺陷的小芯片,这些缺陷会导致内存阵列的该部分无法使用,那么它们将必须被分类用于低端型号 SKU,或者根本不使用。

AMD 迄今为止仅发布了两款 RDNA 3 显卡(Radeon RX 7900 XT 和 XTX),但在这两种型号中,MCD 均具有 16MB 缓存。如果下一轮 Radeon 卡配备 256 位内存总线和 64MB L3 缓存,那么它们也需要使用“完美”的 16MB 芯片。

然而,由于它们的面积非常小,单个 300mm 晶圆可能会产生超过 1500 个 MCD。即使其中 50% 必须报废,这仍然足以提供 125 个 Navi 31 封装。

我们还需要一段时间才能知道 AMD 的设计实际上具有多大的成本效益,但该公司现在和将来都完全致力于使用这种方法,尽管仅限于更大的 GPU。预算 RNDA 3 模型的缓存量要少得多,将继续使用单片制造方法,因为这种制造方法更具成本效益。

英特尔的ACM-G10处理器尺寸为406mm 2,晶体管总数为217亿个,在组件数量和芯片面积方面介于AMD的Navi 21和Nvidia的GA104之间。

这实际上使它成为一个相当大的处理器,这就是为什么英特尔选择 GPU 的市场领域似乎有些奇怪的原因。Arc A770显卡采用完整的 ACM-G10 芯片,与 Nvidia 的 GeForce RTX 3060等显卡进行竞争,后者使用的芯片尺寸和晶体管数量只有英特尔一半。

那么为什么它这么大呢?可能的原因有两个:16MB 的二级缓存和每个 XEC 中的矩阵单元数量非常多。采用前者的决定是合乎逻辑的,因为它减轻了全局内存带宽的压力,但后者很容易被认为对其销售的领域来说是过多的。RTX 3060 有 112 个 Tensor 核心,而 A770 有 512 个 XMX单元。

英特尔的另一个奇怪的选择是使用台积电 N6 来制造 Alchemist 芯片,而不是他们自己的工厂。关于此事的官方声明引用了成本、晶圆厂产能和芯片工作频率等因素。

这表明英特尔的同等生产设施(使用更名后的intel 7节点)将无法满足预期需求,其Alder和Raptor Lake CPU占据了大部分产能。

他们会将 CPU 输出的相对下降以及这对收入的影响与使用 Alchemist 获得的收益进行比较。简而言之,最好付钱给台积电制造新的 GPU。

AMD 利用其多芯片专业知识并开发了用于制造大型 RDNA 3 GPU 的新技术,而 Nvidia 则坚持 Ada 系列的单片设计。GPU 公司在制造超大型处理器方面拥有丰富的经验,但 608mm2 的AD102 并不是其发布的物理上最大的芯片(这一荣誉颁给了826mm2的GA100)。然而,Nvidia 拥有 763 亿个晶体管,其组件数量远远领先于迄今为止任何消费级 GPU。

相比之下,GeForce RTX 3080 及更高版本中使用的 GA102 显得轻量级,只有 268 亿。这 187% 的增长得益于 SM 数量的 71% 增长和 L2 缓存数量的 1500% 的提升。

如此大而复杂的芯片总是难以实现完美的晶圆良率,这就是为什么之前的高端 Nvidia GPU 催生了众多 SKU。通常,随着新架构的推出,他们的专业显卡系列(例如 A 系列、Tesla 等)首先发布。

当 Ampere 发布时,GA102 出现在两款消费级卡中,并最终在 14 种不同的产品中找到了应用。到目前为止,Nvidia 仅选择在两款产品中使用 AD102:GeForce RTX 4090和RTX 6000。不过,后者自 9 月份出现以来一直无法购买。

RTX 4090 使用的芯片更接近分箱过程,禁用了 16 个 SM 和 24MB 二级缓存,而 RTX 6000 仅禁用了两个 SM。这就让人不禁要问:剩下的die在哪里?

但由于没有其他产品使用 AD102,我们只能假设 Nvidia 正在储备它们,尽管其他产品的用途尚不清楚。

GeForce RTX 4080使用 AD103,其尺寸为 379mm2和 459 亿个晶体管,与它的大哥完全不同——更小的芯片(80 个 SM、64MB 二级缓存)应该会带来更好的产量,但同样只有一种产品使用它。

他们还发布了另一款 RTX 4080,其中一款使用了较小的 AD104,但由于收到的批评而取消了发布。预计这款 GPU 现在将用于推出RTX 4070 系列。

Nvidia 显然拥有大量基于 Ada 架构构建的 GPU,但似乎也非常不愿意发货。造成这种情况的原因之一可能是他们正在等待安培驱动的显卡上架;另一个事实是,它主导了一般用户和工作站市场,并且可能认为它现在不需要提供任何其他东西。

但考虑到 AD102 和 103 提供的原始计算能力有了显着提高,Ada 专业卡的数量如此之少就有些令人费解了——该行业总是渴望更多的处理能力。

Superstar DJs: 显示和媒体引擎

当谈到 GPU 的媒体和显示引擎时,与 DirectX 12 功能或晶体管数量等方面相比,它们通常采用幕后营销方法。但随着游戏流媒体行业产生数十亿美元的收入,我们开始看到更多的努力来开发和推广新的显示功能。

对于 RDNA 3,AMD 更新了许多组件,最值得注意的是对 DisplayPort 2.1 和 HDMI 2.1a 的支持。鉴于监督 DisplayPort 规范的组织 VESA在 2022 年底才发布 2.1 版本,GPU 供应商如此迅速地采用该系统是一个不寻常的举动。

新显示引擎支持的最快 DP 传输模式是 UHBR13.5,最大 4 通道传输速率为 54 Gbps。对于标准时序下 4K 分辨率、144Hz 刷新率、无任何压缩的情况来说,这已经足够了。

使用 DSC(显示流压缩:Display Stream Compression),DP2.1 连接允许高达 4K@480Hz 或 8K@165Hz - 比 RDNA 2 中使用的 DP1.4a 有了显著改进。

英特尔的 Alchemist 架构采用具有 DP 2.0(UHBR10,40 Gbps)和 HDMI 2.1 输出的显示引擎,尽管并非所有使用该芯片的 Arc 系列显卡都可以利用最大功能。

虽然ACM-G10并不针对高分辨率游戏,但采用最新的显示连接规格意味着可以在没有任何压缩的情况下使用电子竞技显示器(例如1080p、360Hz)。该芯片可能无法在此类游戏中呈现如此高的帧速率,但至少显示引擎可以。

AMD 和英特尔对 DP 和 HDMI 中快速传输模式的支持正是您对全新架构的期望,因此 Nvidia 选择不对 Ada Lovelace 这样做有点不协调。

AD102 对于所有晶体管(几乎与 Navi 31 和 ACM-G10 加在一起相同)仅具有具有 DP1.4a 和 HDMI 2.1 输出的显示引擎。对于 DSC,前者对于 4K@144Hz 来说已经足够好了,但是当竞争对手支持不压缩的情况下,这显然是错失机会。

GPU 中的媒体引擎负责视频流的编码和解码,所有三个供应商在其最新架构中都拥有丰富的功能集。

在 RDNA 3 中,AMD 添加了针对 AV1 格式的完整同步编码/解码(仅在之前的 RDNA 2 中进行解码)。关于新媒体引擎的信息并不多,只是它可以同时处理两个 H.264/H.265 流,并且 AV1 的最大速率为 8K@60Hz。AMD 还简要提到了“AI 增强”视频解码,但没有提供更多细节。

英特尔的 ACM-G10 具有类似的功能范围,可用于 AV1、H.264 和 H.265 的编码/解码,但与 RDNA 3 一样,细节非常少。对 Arc 桌面显卡中的首批 Alchemist 芯片的一些早期测试表明,媒体引擎至少与 AMD 和 Nvidia 在其先前架构中提供的媒体引擎一样好。

Ada Lovelace 也采用了 AV1 编码和解码,Nvidia 声称新系统的编码效率比 H.264 高 40%,表面上看,使用新格式时视频质量提高了 40%。

高端 GeForce RTX 40 系列显卡将配备配备两个 NVENC 编码器的 GPU,您可以选择以 60Hz 编码 8K HDR,或改进视频导出的并行化,每个编码器同时处理半帧。

GPU 的下一步是什么?

桌面 GPU 市场上已经有三个供应商了,很明显,每个供应商都有自己的图形处理器设计方法,尽管英特尔和 Nvidia 也采取了类似的思维方式。

对于他们来说,Ada 和 Alchemist 在某种程度上是万事通,可用于各种游戏、科学、媒体和数据工作负载。ACM-G10 中对矩阵和张量计算的高度重视以及不愿完全重新设计其 GPU 布局表明英特尔更倾向于科学和数据,而不是游戏,但考虑到这些领域的潜在增长,这是可以理解的。

对于最后三种架构,Nvidia 专注于改进已经很好的架构,并减少整体设计中的各种瓶颈,例如内部带宽和延迟。虽然 Ada 是对 Ampere 的自然改进(Nvidia 多年来一直遵循这一主题),但当你观察晶体管数量的绝对规模时,AD102 却显得异常进化。

与 GA102 相比,差异非常显着,但这种巨大的飞跃引发了许多问题。首先,对于 Nvidia 的最高端消费产品来说,AD103 是否是比 AD102 更好的选择?

与 RTX 4080 中使用的 AD103 相比,AD103 的性能比 RTX 3090 有了相当大的改进,并且与它的大哥一样,64MB 的二级缓存有助于抵消相对较窄的 256 位全局内存总线宽度。它的尺寸为 379mm2,比 GeForce RTX 3070 中使用的 GA104 小,因此制造利润比 AD102 高得多。它还包含与 GA102 相同数量的 SM,并且该芯片最终在 15 种不同的产品中得到了应用。

另一个值得问的问题是,Nvidia 在架构和制造方面将走向何方?他们能否在仍坚持使用单片芯片的情况下实现类似的缩放水平?

AMD 对 RDNA 3 的选择凸显了竞争的潜在路线。通过将芯片中规模最差的部分(在新工艺节点中)转移到单独的小芯片中,AMD 已经能够成功地延续 RDNA 和 RDNA 2 之间的大型制造和设计飞跃。

虽然它不像 Nvidia 的 AD102 那么大,但 AMD Navi 31 的硅片价值仍然高达 580 亿个晶体管,是 Navi 21 的两倍多,也是我们最初的 RDNA GPU Navi 10 的 5 倍多(尽管这不是 Navi 21 的两倍)。

AMD 和 Nvidia 的成就并不是孤立取得的。GPU 晶体管数量如此大幅增加的唯一原因是台积电和三星之间作为半导体设备主要制造商的激烈竞争。两者都致力于提高逻辑电路的晶体管密度,同时继续降低功耗。台积电对于当前的节点改进及其下一步的主要工艺有明确的路线图。

目前尚不清楚 Nvidia 是否会效仿 AMD 的做法,并在 Ada 的继任者中采用小芯片布局,但接下来的一两年可能会起到决定性作用。如果 RDNA 3 被证明在财务上取得了成功,无论是在收入还是总出货量方面,那么 Nvidia 很可能会效仿。

然而,第一个使用 Ampere 架构的芯片是 GA100——一款数据中心 GPU,尺寸为829mm2 ,拥有 542 亿个晶体管。它由 TSMC 使用其 N7 节点制造(与 RDNA 和大多数 RDNA 2 系列相同)。使用 N4 来制造 AD102,使得 Nvidia 能够设计出晶体管密度几乎是其前身的两倍的 GPU。

在下一个架构中使用 N2 可以实现这一目标吗?有可能,但缓存的大幅增长(扩展性非常差)表明,即使台积电在未来的节点上取得了一些引人注目的成绩,控制 GPU 大小也将变得越来越困难。

英特尔已经在使用小芯片,但仅限于其巨大的Ponte Vecchio数据中心 GPU。由47块不同的tiles组成,当中有些是台积电制造的,有些是英特尔自己制造的,其参数相当高。例如,完整的双 GPU 配置拥有超过 1000 亿个晶体管,这使得 AMD 的 Navi 31 看起来非常“小”。当然,它不适用于任何类型的台式电脑,严格来说也“不仅仅是”GPU——这是一个数据中心处理器,重点关注矩阵和张量工作负载。

在转向“Xe Next”之前,其 Xe-HPG 架构至少还要进行两次修订,我们很可能会在英特尔消费类显卡中看到平铺的使用。

不过,目前,我们将让 Ada 和 Alchemist 使用传统的单片芯片,而 AMD 则将混合芯片系统用于中高端卡,并为其预算 SKU 使用单芯片。

到本世纪末,我们可能会看到几乎所有类型的图形处理器,它们都是由精选的不同tile和小芯片构建而成,全部使用各种工艺节点制成。GPU 仍然是台式电脑中最引人注目的工程壮举之一——晶体管数量没有显示出增长放缓的迹象,而今天普通显卡的计算能力在大约 10 年前只能是梦想。

让我们进入下一场三向架构之战吧!